Institut für Informatik und Praktische Mathematik der Christian-Albrechts-Universität zu Kiel Olshausenstr. 40 D – 24098 Kiel

# Formal Methods and the Development of Dependable Systems

Jan Peleska

e-mail: jp@informatik.uni-bremen.de

Bericht Nr. 9612 Dezember 1996

Dieser Bericht enthält die Habilitationsschrift des Verfassers.

Referent: Prof. Dr. Willem-Paul de Roever Koreferenten: Prof. Dr. Manfred Broy, Prof. Dr. Mathai Joseph, Prof. Dr. Hans Langmaack, Dr. Tech. Anders P. Ravn

## **Preface**

This *Habilitationsschrift*<sup>1</sup> focuses on methods for the development of dependable software-based systems. It summarises, discusses and extends my publications cited in the bibliography, which reflect the efforts and experiences gained in this field during the last decade, working as a software engineer, project leader and manager at *Philips GmbH*, *Deutsche System-Technik GmbH* and as a consultant for various other companies.

The applications to be discussed as examples will mostly be chosen from the field of non-military information and control systems. Such a specialisation appears to be necessary, because the type of application influences the objectives to be met by dependability mechanisms. For example, in dependable and secure military applications (see [50]), the aspect of confidentiality (mandatory access control, covert channels etc.) plays a much more important rôle than for a railway control system. As a consequence, different application areas lead to different approaches with respect to system design, development techniques and underlying specification and design methods.

The methodological framework used is based on *Formal Methods*. I would like to point out that though my university education was rather theoretical (see [72]), the motivation to use theory for building software was purely motivated by the fact that the informal heuristics applied for constructive or analytic software quality assurance are completely insufficient when applied to systems where correctness of software really matters. The key ideas described in the chapters to follow might be summarised by three statements reflecting my conviction how the software crisis should be tackled in the future:

- The complexity of today's applications can only be managed by applying a combination of methods, each of them specialised to support specific development steps in an optimised way during the system development process.

- The application of formal methods should be supported by *development standards*, i. e., explanations or "recipes" showing how to apply the methods in the most efficient way to a specific type of development task. Indeed, tool support and development standards may be regarded as essential for the success of formal methods in an industrial context.

- The application of formal methods for the development of dependable systems will only become cost-effective if the degree of *re-usability* is increased by means of re-usable (*generic*) specifications, re-usable proofs, code and even re-usable development processes.

As a consequence, the objective of this *Habilitationsschrift* is not to introduce new specification languages, proof techniques *et cetera*, but to show how new combinations of existing methods can be applied more efficiently to solve problems in the field of dependable systems.

<sup>&</sup>lt;sup>1</sup>Postdoctoral thesis, required in Germany for the qualification of a university lecturer; since the English language does not provide a proper counterpart for this term, we keep the German expression instead of using an English circumscription.

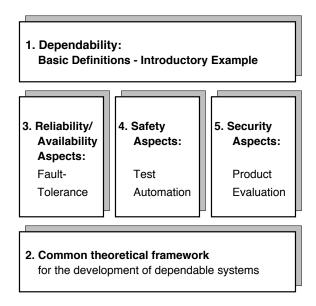

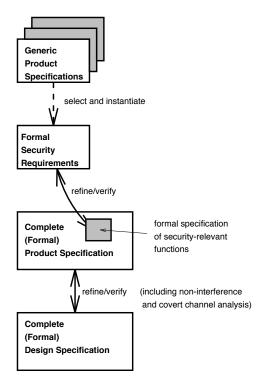

The "architecture" of this work is depicted in Figure 0.1. In the introductory Chapter 1 some basic definitions used in the context of dependability are presented and discussed, since the "invasion" of software into this field has forced specialists to re-interpret important terms previously used only in the context of mechanical and electrical engineering. Moreover, an example is given which reflects the complexity to be encountered when trying to combine different dependability mechanisms (e. g. a fault-tolerant protocol together with a security mechanism) in order to "add up" the benefits of these mechanisms in one system. In Chapter 2 I will describe an approach for the systematic formal development of dependable systems. This approach offers a design technique systematically dealing with situations where not just one threat to system dependability but a collection of threats has to be taken into account. At the same time it is embedded in a general development framework that has proved to be practical for large projects and is accepted by (at least the more enlightened species of) today's software engineers in industry. This embedding associates a theoretic foundation with an informal development standard, using selected formal methods to produce the contents of the documents pre-defined in the standard. The example of Chapter 1 is used to demonstrate how the approach can be put into practice. This work has been mainly motivated by my cooperation with ELPRO LET GmbH and the University of Oldenburg in the field of distributed railway interlocking systems.

Figure 0.1: "Architecture" of the *Habilitationsschrift*.

Chapters 3 to 5 focus on specific aspects and applications in the field of dependable systems: reliability/availability, safety and security. In Chapter 3 the formal specification and verification of a dual computer system is described, where the reliability of the system is ensured by means of a fault-tolerance mechanism. The underlying design and verification concepts have been worked out during my time with Philips, where I was confronted with the development of a fault-tolerant database server. In Chapter 4 a concept for the automated test of safety-critical embedded systems will be introduced. The concept and the corresponding tool support have been developed for and applied in the field of railway interlocking systems for small private railways or tramways. For these systems, the degree of complexity is considerably lower than in the case of large-scale railway networks. Furthermore, safety aspects play the dominant rôle, while reliability and availability are subordinate aspects. Therefore

we can achieve a much higher degree of automation for the test and verification process than for the case of dependable systems in general. In Chapter 5 security aspects of dependable systems are investigated. Here we concentrate on the evaluation of commercially available IT security products. The objective of this evaluation is to certify in a trustworthy way that the system is capable to protect its users against the specified types of security attacks. This work has been initiated while I was manager of a department at DST that was specialised on developing dependable systems. Associated with the department was an evaluation laboratory which was accredited at the  $Bundesamt\ f\"ur\ Sicherheit\ in\ der\ Informationstechnik\ BSI$ , the German authority for the certification of IT security products.

You may have noticed that I did not use the Preface to give a "sales talk" about how much we are threatened by software of insufficient quality and how only formal methods can deliver us from this evil. Firstly, I assume that this *Habilitationsschrift* will only be read by experts anyway, and either you will already be a member of the formal methods community or you will be too much of an expert to be convinced by my arguments. Secondly, I have the impression that the common understanding about the *status quo* of the software crisis, what formal methods can do about it and where the limitations of formal methods lie has improved very quickly during the last five years. This even holds for hard-boiled software practitioners to be encountered in software industry. If you still feel like reading some motivating thoughts about all this, I am sure the articles of Gibbs [31], Heisel and Weber-Wulff [38] and the Hamer-Hörcher-Peleska formal methods primer [79] will satisfy your needs.

**Acknowledgements** While writing (and re-writing) this *Habilitationsschrift* I have been very aware of how much we depend on the support of other people, whenever a sincere effort shall meet its goals. I would like to express my gratitude to all those who have helped me during the completion of this work, for their advice, both technical and personal, their encouragement, their patience and sometimes simply for the splendid time we've had together:

Alexander Baer, Walter Benz, Dines Bjørner, Chris Brink, Manfred Broy, Bettina and Karl-Heinz Buth, Rachel Cardell-Oliver, Di Dixon, Manfred Endreß, Ute Hamer, Ilse and Heinz-Otto Hamer, Ute Hammerich, Rait Harnett, Maritta Heisel, Mike Hinchey, Tony Hoare, Hans-Martin Hörcher, Kees Huizing, Mathai Joseph, Dagmar König, Bernd Krieg-Brückner, Hans Langmaack, Maureen Le Sar, Erich Mikk, Ernst-Rüdiger Olderog, Astrid Peleska, Erika and Viktor Peleska, Carsta Petersohn, Erhard Pompe, Anders P. Ravn, Hans Rischel, Corinne and Willem-Paul de Roever, Fred Schindler, Michel Schrönen, Michael Siegel, Mike Spivey, Änne Straßner, Jan Vytopil, Jim Woodcock, Margarete Worm

# Contents

|   | Pre  | face        |                                                          | i  |

|---|------|-------------|----------------------------------------------------------|----|

| 1 | Intr | atroduction |                                                          |    |

|   | 1.1  | Deper       | ndability — Basic Definitions and Concepts               | 1  |

|   | 1.2  | Comb        | ination of Dependability Mechanisms — Case Study Part I  | 5  |

| 2 | A F  | ramev       | work for the Development of Dependable Systems           | 14 |

|   | 2.1  | Overv       | iew                                                      | 14 |

|   | 2.2  | Relate      | ed Industrial Projects                                   | 15 |

|   | 2.3  | Stand       | ards for the Development of Dependable Systems           | 16 |

|   |      | 2.3.1       | Overview                                                 | 16 |

|   |      | 2.3.2       | System Development According to the V-Model              | 18 |

|   | 2.4  | A For       | mal Approach for the Development of Dependable Systems   | 21 |

|   |      | 2.4.1       | Selection Criteria for the Formal Method                 | 21 |

|   |      | 2.4.2       | System Requirements                                      | 22 |

|   |      | 2.4.3       | System Architecture                                      | 27 |

|   |      | 2.4.4       | Verification on System Level                             | 29 |

|   |      | 2.4.5       | Recursive Application of the Development Procedure       | 31 |

|   | 2.5  | Comb        | ination of Dependability Mechanisms — Case Study Part II | 32 |

|   |      | 2.5.1       | System Requirements                                      | 33 |

|   |      | 2.5.2       | System Architecture                                      | 39 |

|   |      | 2.5.3       | Verification on System Level                             | 43 |

|   |      | 2.5.4       | Recursive Application of the Development Procedure       | 49 |

|   |      | 2.5.5       | Verification of Deadlock Freedom                         | 51 |

|   | 2.6  | Discus      | ssion and Future Work                                    | 54 |

<u>V1</u> <u>CONTENTS</u>

| 3                                                                   | Rel  | iability                                                        | and Availability Aspects: Fault-Tolerance                    | <b>5</b> 6 |

|---------------------------------------------------------------------|------|-----------------------------------------------------------------|--------------------------------------------------------------|------------|

|                                                                     | 3.1  | Overv                                                           | iew                                                          | 56         |

|                                                                     | 3.2  | Related Industrial Projects                                     |                                                              |            |

|                                                                     | 3.3  | 3 Case Study: Fault-Tolerant Server System With Repair          |                                                              |            |

|                                                                     |      | 3.3.1                                                           | Informal Problem Description                                 | 59         |

|                                                                     |      | 3.3.2                                                           | Presentation of the Implementation                           | 60         |

|                                                                     |      | 3 <b>.</b> 3.3                                                  | System Requirements                                          | 66         |

|                                                                     |      | 3.3.4                                                           | System Architecture                                          | 68         |

|                                                                     |      | 3.3.5                                                           | Verification on System Level                                 | 70         |

|                                                                     |      | 3.3.6                                                           | Sub-System Design                                            | 80         |

|                                                                     |      | 3.3.7                                                           | Process Design of DCP                                        | 80         |

|                                                                     |      | 3.3.8                                                           | Verification of Process Design for DCP                       | 81         |

|                                                                     | 3.4  | Verific                                                         | cation of Behavioural Properties for Sequential Processes    | 87         |

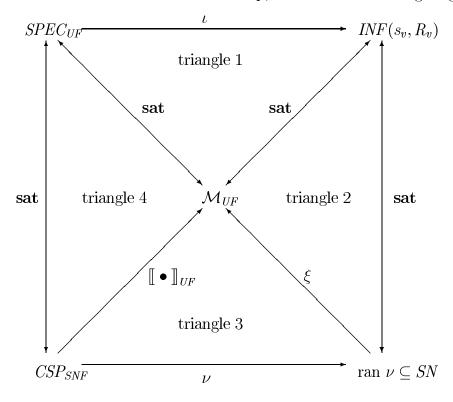

|                                                                     |      | 3.4.1                                                           | Sequential Nondeterministic Programs                         | 87         |

|                                                                     |      | 3.4.2                                                           | Sequential CSP Processes in Normal Form                      | 88         |

|                                                                     |      | 3.4.3                                                           | Mapping Normal Form Processes to Sequential Programs         | 91         |

|                                                                     |      | 3.4.4                                                           | Mapping Behavioural Specifications to Invariants             | 97         |

|                                                                     |      | 3.4.5                                                           | Mapping Sequential Programs into the Failures Model          | 97         |

|                                                                     |      | 3.4.6                                                           | Establishing Behavioural Properties of Normal Form Processes | 99         |

|                                                                     | 3.5  | Discus                                                          | ssion and Future Work                                        | 100        |

| 4                                                                   | Safe | ${ m ety}~{ m As}_{ m I}$                                       | pects: Test Automation for Reactive Systems                  | 102        |

|                                                                     | 4.1  | Overv                                                           | iew                                                          | 102        |

|                                                                     | 4.2  | Relate                                                          | ed Industrial Projects                                       | 103        |

| 4.3 Test Automation for Reactive Systems – Motivation and Basic Co. |      | Automation for Reactive Systems – Motivation and Basic Concepts | 105                                                          |            |

|                                                                     |      | 4.3.1                                                           | Motivation                                                   | 105        |

|                                                                     |      | 4.3.2                                                           | Formal Methods for Tool Qualification                        | 107        |

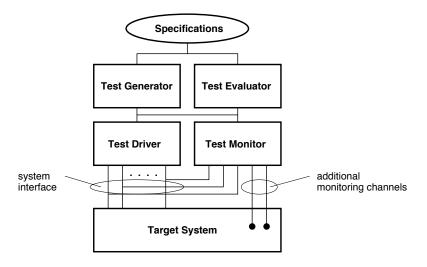

|                                                                     |      | 4.3.3                                                           | Logical Building Blocks of a Test Automation System          | 107        |

|                                                                     | 4.4  | Testin                                                          | g Terminology                                                | 109        |

|                                                                     | 4.5  | Trustv                                                          | worthy Testing – Untimed Case                                | 111        |

|                                                                     |      | 4.5.1                                                           | Motivation and Conceptual Background                         | 111        |

|                                                                     |      | 4.5.2                                                           | CSP, Refinement and the Relation to Testing Methodology      | 113        |

|                                                                     |      |                                                                 |                                                              |            |

<u>CONTENTS</u> VII

|         |     | 4.5.3   | Trustworthy Test Drivers                                        | 126 |

|---------|-----|---------|-----------------------------------------------------------------|-----|

|         | 4.6 | Discus  | ssion and Future Work                                           | 138 |

| 5       | Sec | urity A | Aspects: Trustworthy Evaluation of IT Security Products         | 141 |

|         | 5.1 | Overv   | iew                                                             | 141 |

|         | 5.2 | Produ   | act Evaluation in Industry – Practical Experiences              | 142 |

|         | 5.3 | A For   | mal Evaluation Approach                                         | 144 |

|         | 5.4 | Exam    | ple: Security Evaluation Based on Generic Formal Specifications | 145 |

|         |     | 5.4.1   | Functionality Class F-C1: Discretionary Access Control          | 145 |

|         |     | 5.4.2   | Formalisation of the F-C1 Requirement                           | 146 |

|         |     | 5.4.3   | Clarification of Ambiguities in Natural-Language Requirements   | 148 |

|         | 5.5 | A For   | mal Evaluation Example                                          | 149 |

|         |     | 5.5.1   | UNIX Access Control Lists                                       | 149 |

|         |     | 5.5.2   | Formalisation of the ACL Model                                  | 150 |

|         |     | 5.5.3   | Instantiation of the Generic Specification                      | 152 |

|         |     | 5.5.4   | Abstraction Relation Between F-C1 Model and ACL Model           | 152 |

|         |     | 5.5.5   | Verification of the Refinement                                  | 155 |

|         | 5.6 | Discus  | ssion and Future Work                                           | 157 |

| ${f A}$ | Glo | ssary ( | of Symbols                                                      | 166 |

| В       | A C | )uick-F | Reference Guide to CSP                                          | 168 |

# List of Figures

| 0.1 | "Architecture" of the <i>Habilitationsschrift</i>                                                                                                                                              | ii  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 1.1 | Types of system behaviour                                                                                                                                                                      | 4   |

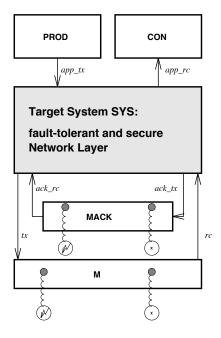

| 1.2 | Context of the target system (network layer) and its environment                                                                                                                               | 5   |

| 1.3 | Unreliable transmission media and alternating bit protocol implemented by $ABP\_TX, ABP\_RC$                                                                                                   | 7   |

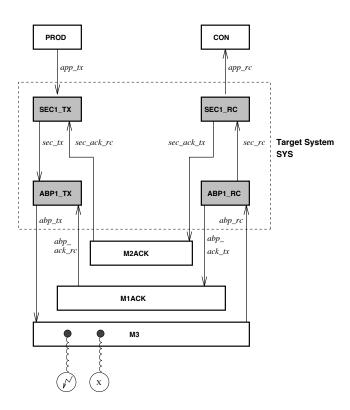

| 1.4 | Security layer $SEC1\_TX$ , $SEC1\_RC$ to protect the application layer against eavesdropping and tampering on $M2$ by agent X                                                                 | 9   |

| 1.5 | Naive combination of security layer and network layer with unreliable and insecure medium $M3$ . (For the sake of simplicity, $M1ACK$ and $M2ACK$ are assumed to be ideal transmission media.) | 12  |

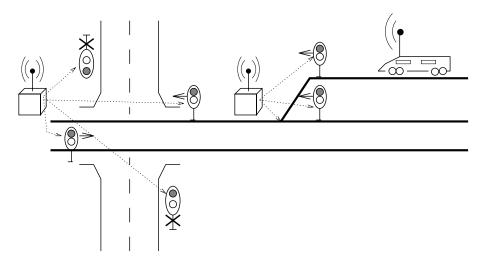

| 2.1 | System overview of a distributed interlocking system                                                                                                                                           | 15  |

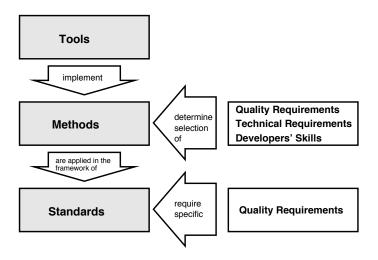

| 2.2 | Relationship between standards, methods and tools                                                                                                                                              | 17  |

| 2.3 | System configuration for the case study, part II                                                                                                                                               | 33  |

| 2.4 | System architecture consisting of network layer and security layer                                                                                                                             | 40  |

| 2.5 | Internal threat analysis: Possible loss of data on channel $abp\_rc.$                                                                                                                          | 43  |

| 2.6 | Correct combination of a new security layer with re-used network layer                                                                                                                         | 50  |

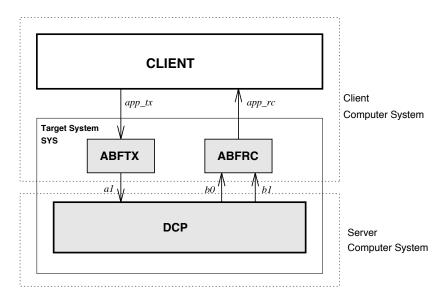

| 3.1 | Client-server system                                                                                                                                                                           | 59  |

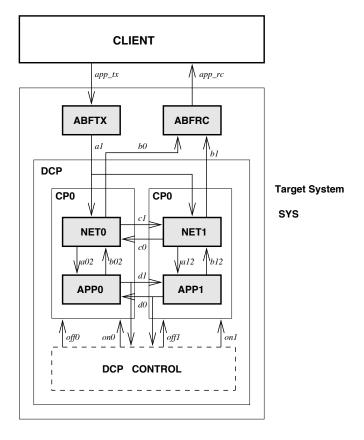

| 3.2 | Full architecture of the fault-tolerant server system                                                                                                                                          | 61  |

| 3.3 | Server system architecture                                                                                                                                                                     | 68  |

| 4.1 | Logical building blocks of a test automation system                                                                                                                                            | 108 |

| 5.1 | IT security evaluation approach                                                                                                                                                                | 144 |

# 1. Introduction

## 1.1 Dependability — Basic Definitions and Concepts

Throughout this work, we will follow Laprie's terminology [56, 57, 58] with respect to dependability and related terms.

Generally speaking, dependability is the capability of a system to deliver the specified application services during its period of operation. This definition emphasizes two aspects that influence the design, the implementation and our reasoning about system "correctness" in a crucial way:

- Dependability does *not* forbid the occurrence of failures in general. Instead, it requires that the *application service*, i. e., the functionality required by the end user of the system is delivered as specified.

- Delivery of service is only required to the extent covered by the specification. This is a very reasonable requirement otherwise the supplier would never have a chance to prove that the system has been completed and the customer's requirements have been implemented. On the other hand, the approach is only useful, if the technical contents of a specification document reflecting how a system will behave according to the developers' understanding is consistent with the end user's intuitive understanding of how the system should behave. As a consequence, the specification phase has become the most critical phase of the whole system development life cycle.

Laprie identified four attributes which characterise the dependability of a system: (1) A safe system cannot assume states that are regarded as "catastrophic" from the point of view of the application. This means that the system will only perform transitions into states satisfying the specified invariants, perform calculations that are correct with respect to the specification and output data fulfilling the desired integrity constraints. Safety does not guarantee that a desired calculation and the corresponding output will always be produced. This aspect is covered by the following two attributes: (2) Reliability is a characteristic specifying the probability that a system will deliver its service for a given period of time<sup>1</sup>. (3) Availability is a measure reflecting the probability that the system will be available at a certain point in time. (4) Finally, Security reflects the capability of the system to protect the application against damage arising from accidental or malicious human interaction. All dependability attributes refer to the specified application, and this is the very premise for the notion of fault-tolerance: A dependable system may be subject to various internal defects, as long as these problems do not affect the application behaviour.

For the security attribute, a further characterisation has been provided: According to the standards [17, 28, 29, 47, 111] the notion of *Information Technology (IT) Security* is defined

<sup>&</sup>lt;sup>1</sup>For example, the *mean time between failure (MTBF)* is a reliability measure.

2 1. Introduction

by the attributes Confidentiality (prevention of unauthorised disclosure of information), Integrity (prevention of unauthorised modification of information) and Availability (prevention of unauthorised withholding of information or resources)<sup>2</sup>. IT security focuses on the damage that can be caused by humans. In [17, p. 3] this is made explicit by defining IT security as "...protection of information ...by countering threats to that information arising from human activities whether malicious or otherwise." There is at least one good reason to distinguish between threats arising from technical deficiencies and those arising from human activities: In many cases technical faults can be considered as accidental events and therefore adequately modelled by statistical approaches. These modelling techniques will fail, however, when being applied to the behaviour of malicious human intruders, who can try to cause damage in a systematic way.

Since the definition of dependability is intended to be applicable to a wide spectrum of systems and the aspects of dependability are intended to be describable by a wide range of formalisms, Laprie's definitions are of informal nature. It is useful to relate them to the formal notions of safety and liveness. Recall that in the context of formal methods a specification item S is a safety property, if any sequence of events or transitions etc. violating S contains a prefix all of whose infinite extensions violate S. A specification item L is called a liveness property, if any arbitrary finite sequence of events can be extended to an infinite sequence satisfying L [62, p. 303]. Obviously, the dependability attribute safety is also a safety property in the sense of formal methods. The situation is less obvious for availability: In the context of hard real-time systems, it is best interpreted as another safety property, because the availability of a service is then interpreted as "available within n time units", and an assertion saying that the service will "finally" be available is not helpful at all. For less time-critical applications, however, the notion of availability might be associated with "the service will not be blocked forever" or "the service will be activated sufficiently often", and these are liveness properties. As a consequence, the formalisation of the availability definition depends on the specific application. Reliability is only indirectly related to safety and liveness: Intuitively, this dependability attribute describes the possibilities of the system to "switch" from one specified behaviour to another behaviour which is regarded as exceptional. Of course, both behaviour specifications can be decomposed into safety and liveness properties. The confidentiality and integrity aspect of security is a safety property. For the availability aspect of security the same considerations apply as for availability in general.

The notion of security is a "new" dependability attribute, due to Laprie. For example, in the definition given 1985 in [7], security is not yet mentioned, and even in a fairly recent survey [107] on real-time computing the authors state that ...it is not very important in a real-time operating system to provide extensive support for ...security. I think that this fact is characteristic for the type of systems designers had – and sometimes still have – in mind when coining the notion of dependability in the context of computer science for the first time. The major threats to dependability were hardware and software errors and external physical events. Threats caused by humans were thought to be similar to natural disasters like acts of vandalism. The more "subtle" aspects of security were not considered as

<sup>&</sup>lt;sup>2</sup>Obviously, these attributes introduce redundancy in the dependability definition, since availability has already been introduced as a main attribute of dependability and integrity can be regarded as a safety aspect. These issues have been discussed by Jonsson and Olovsson [53]. However, it is not our objective to try and improve existing definitions, but to find trustworthy ways how to build systems according to given dependability requirements.

relevant in the early eighties. On the other hand, it has always been an obvious requirement that a dependable system should also be secure because otherwise, a human attacker might systematically damage the integrated dependability mechanisms. However, in the "early times" of dependable computerised systems, security issues could often be ignored in the software design, because the operational environment was automatically secure, i. e. did not possess any interfaces accessible to a human attacker. In recent years, a growing demand for open and/or distributed dependable systems became apparent. Obviously, these new key attributes force us to treat security as a global system issue which has to be covered by protective mechanisms both in the operational environment and in the software. Examples for such projects are given in Chapter 2 and in [78]. From my experience it is interesting to note that the demand for open, distributed dependable systems came from two sides:

- In the "classical" application domains of dependable systems openness and distribution have often been introduced to reduce costs by providing a system architecture that can be customised and extended more easily.

- In less critical applications dependability became an important aspect *a posteriori*, in order to reduce costs by increasing the operational availability and to avoid loss or corruption of valuable data. These systems were often open and distributed by their very nature, and the new dependability features had to be fitted into this existing architectural framework.

I will use the term *classical dependability* when referring to safety, reliability and availability only.

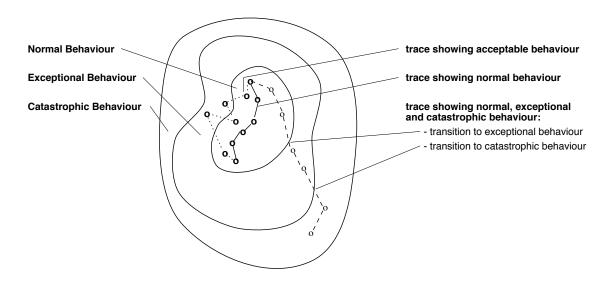

To illustrate the design tasks to be tackled for the development of dependable systems the classification of system behaviours depicted in Figure 1.1 will be used. In absence of any undesired (internal or external) events, the system executes<sup>3</sup> normal behaviour. In presence of undesired events the system may perform an execution possibly differing from that of the undisturbed system. Now there are two possibilities: In the first case, an undesired event impairs the functionality of the system in a way that can be tolerated or might even be unobservable in the application layer. In this case the system shows exceptional behaviour. If the system performs an execution showing normal and/or exceptional behaviour, this is summarised as acceptable behaviour. In the second case, the occurrence of the undesired event corrupts the application functionality in a way that cannot be tolerated. This is called catastrophic behaviour. Although the above classification has been introduced in [59] to describe concepts of fault-tolerance only, it fits very well to deal with dependability as a whole.

In order to prevent undesired events from leading to catastrophic system behaviour, system designers must anticipate the possibility of their occurrence and incorporate protective mechanisms in their development concepts. The potential occurrence of any undesired event will be called a *Threat* or a *Fault Hypothesis*. If it is necessary to distinguish between aspects of classical dependability and security, we will denote the fault hypotheses anticipating human interactions as *Security Threats*. The actual occurrence of any undesired event is called a

<sup>&</sup>lt;sup>3</sup>Depending on the formalism used, an execution may be a modelled as a *trace of events*, hiding internal state information, or as a sequence of *state transitions* triggered by events. For hybrid systems, the execution is modelled as some type of *trajectory*, traversing an appropriate space-time model spanned by state and time parameters.

4 1. Introduction

Figure 1.1: Types of system behaviour.

Fault. Faults caused by security threats are termed Human-Made Faults; we will also use the more suggestive term Security Attack and summarise human-made and other faults as Exceptions. The process of anticipating exceptions will be denoted as Threat Analysis. If an exception causes a transition into an undesired system state, this state is called an Error. If due to the occurrence of exceptions and errors a specified service to be performed by a (sub-)system cannot execute as required, this is called a Failure. In the context of real-time systems it is often necessary to distinguish Value Failures, where incorrect data is produced or processed by the system from Timing Failures, where correct data appears at the wrong time.

The means to prevent faults, errors and failures are Fault Avoidance (building "perfect" hardware and software components by means of special construction techniques), Fault Tolerance (use of techniques allowing the continuation of service in presence of faults), Verification (detection and removal of errors by means of analytic techniques) and Error Forecasting (analysis of the impact of specific errors and of the probability for their occurrence). The objects implemented to prevent the undesired consequences of security attacks are called Security Mechanisms.

To model the system behaviour in presence of exceptions, two main techniques have been used by different authors:

- Explicit specification, for example by specifying the system and the impact of exceptions in terms of a process algebra. This method will be demonstrated in the next section. Further applications are presented in Chapter 3.

- Behavioural specifications:<sup>4</sup> The system behaviour and the impact of anticipated exceptions is described by predicates on traces of events or executions of a transition system [70, 104].

<sup>&</sup>lt;sup>4</sup>Following Jones [52], we also use the term *implicit* specifications.

# 1.2 Combination of Dependability Mechanisms — Case Study Part I

While many publications investigate isolated dependability aspects<sup>5</sup>, relatively few of them are concerned with combinations of these aspects. I am convinced, however, that it is just this combination that introduces a new degree of complexity in the field of dependable systems, because

- it can be dangerous to combine two dependability mechanisms in a naive way and hope that the resulting system will automatically possess the strength of both mechanisms,

- the design of correctly cooperating dependability mechanisms is likely to differ strongly from solutions where only one isolated mechanism is required.

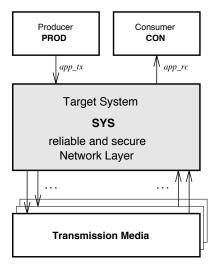

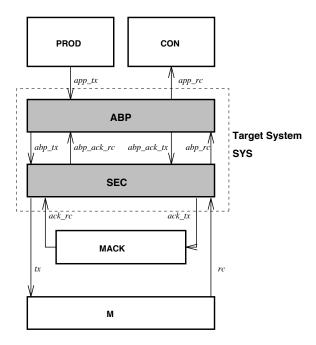

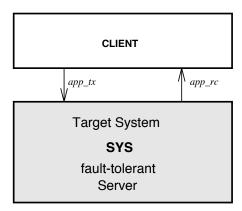

To support these theses, we will now analyse a case study focusing on the development of a network protocol which is dependable in the presence of both unreliable and insecure transmission media (Figure 1.2). The case study is a revised version of the example worked out in [78]. In the remaining part of this chapter it will serve to illustrate the complexity to be expected when more than one dependability threat is involved: two mechanisms correctly defending the system against the reliability threat and the security threat alone, respectively, will result in an *unreliable* protocol when combined in a "naive" way. This failure to construct "globally" dependable mechanisms from isolated solutions in an intuitive way will motivate the systematic approach for the development of dependable systems as introduced in Chapter 2.

Figure 1.2: Context of the target system (network layer) and its environment.

In the examples to follow the number of transmission media and their various deficiencies will vary in order to illustrate different aspects of dependability. The dependability requirement will always remain the same, however:

• Construct SYS in such a way that the resulting communication service will act for producer PROD and consumer CON as a FIFO buffer without loss of data or corruption of messages.

<sup>&</sup>lt;sup>5</sup>Rushby [102] has collected a comprehensive bibliography.

6 1. Introduction

I will use CSP (Communicating Sequential Processes) as introduced by Hoare [44] to specify and reason about system behaviour. Correctness properties will be expressed by means of failures-divergence refinement relating the CSP process expressing correct behaviour to the protocol solutions proposed in the examples. The refinement steps presented have been mechanically checked using the FDR tool [27]. FDR allows to verify refinement properties by means of complete model checking for CSP systems consisting of cooperating finite-state sequential processes. The specification by explicit processes only serves for illustration purposes in these examples. In Chapter 2, a behavioural specification style will be used which is more adequate for the abstract description of large systems.

The informal dependability requirement can be specified by relating an implementation X to the explicit CSP process<sup>6</sup> FIFO defined as

$$\alpha(FIFO) = \{ \mid app\_tx, app\_rc \mid \}$$

$$FIFO = BUFF(\langle \rangle)$$

$$BUFF(s) = (\#s < N)\&app\_tx?x \rightarrow BUFF(s^{\langle \rangle})$$

$$[]$$

$$(\#s > 0)\&app\_rc!(head(s)) \rightarrow BUFF(tail(s))$$

which represents a FIFO buffer of finite capacity N: Any X consisting of the transmission media and the protocol layer SYS used in the implementation has to satisfy

$$FIFO \sqsubseteq_{FD} X \setminus (\alpha(X) - \{| app\_tx, app\_rc |\})$$

where  $P \sqsubseteq_{FD} Q$  means that P is refined by Q in the failures-divergence model of CSP.

Example 1.1 (Communication disturbed by unreliable media) We first consider the case where only unreliable transmission media are available, behaving as follows:

- 1. Fault hypothesis: The medium may lose messages. The number of consecutive input messages that the medium may lose is bounded by a number  $maxLoss \ge 0$ .

- 2. The medium does not change the values of messages delivered to the consumer.

- 3. The medium delivers messages in the order of the corresponding inputs.

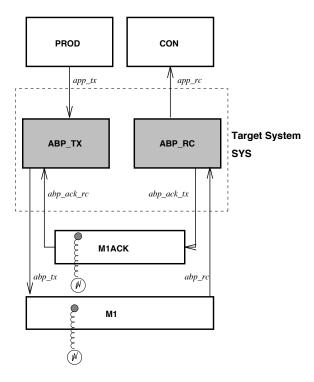

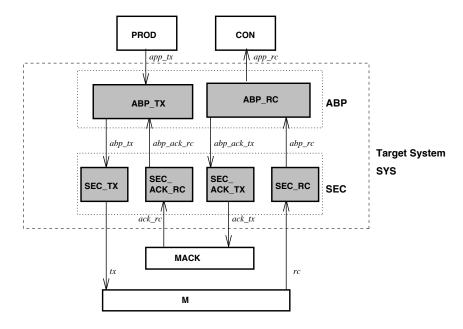

In order to design a fault-tolerant network layer taking into account the above fault hypothesis, the architecture shown in Figure 1.3 is used (the "lightning" symbols indicating the possibility of data losses). M1, M1ACK are two instances of the unreliable medium. Their behaviour according to the above assumptions can be expressed by the following CSP processes:

<sup>&</sup>lt;sup>6</sup>We use *communication guards*: in an expression b&c, the communication via channel c is refused by the process, if the Boolean expression b evaluates to false. {[c,d,...]} denotes the set of channel events { $c.x_1, c.x_2,..., d.y_1, d.y_2,...$ },  $x_i$  and  $y_j$  are values of the channel alphabets of c and d, respectively.

Figure 1.3: Unreliable transmission media and alternating bit protocol implemented by  $ABP\_TX$ ,  $ABP\_RC$ .

```

\begin{split} M1 &= M1(maxLoss) \\ M1(n) &= abp\_tx?(b,x) \to \\ & (\textbf{if } n = 0 \textbf{ then} \\ & (abp\_rc!(b,x) \to M1(maxLoss)) \\ & \textbf{else} \\ & (abp\_rc!(b,x) \to M1(maxLoss) \\ & \sqcap \\ & M1(n-1))) \\ \\ M1ACK &= M1ACK(maxLoss) \\ \\ M1ACK(n) &= abp\_ack\_tx?b \to \\ & (\textbf{if } n = 0 \textbf{ then} \\ & (abp\_ack\_rc!b \to M1ACK(maxLoss)) \\ & \textbf{else} \\ & (abp\_ack\_rc!b \to M1ACK(maxLoss)) \\ & \sqcap \\ & M1ACK(n-1))) \end{split}

```

To construct a reliable network layer on top of M1, M1ACK, we use the well-known alternating bit protocol (e. g., see [64, 104] for two alternative versions of the protocol) consisting of a transmitter  $ABP\_TX$  and a receiver  $ABP\_RC$  with  $SYS = (ABP\_TX \parallel ABP\_RC)$ .  $ABP\_TX$  receives data from the producer, attaches a bit value alternating with each new

8 1. Introduction

message accepted on  $app\_tx$  and sends it via M1 to  $ABP\_RC$ . The receiver passes data via  $app\_rc$  to the consumer, if the attached bit has the expected value in the alternating sequence. In any case  $ABP\_RC$  sends the bit value received back to  $ABP\_TX$  via medium M1ACK to acknowledge reception. In our ABP solution  $ABP\_TX$  will continuously transmit the actual (bit, data)-package until it receives an acknowledgement with the same bit value. The corresponding CSP processes are

```

ABP\_TX = ABP\_TX(1)

ABP\_TX(bit) = app\_tx?x \rightarrow ATX((1-bit), x)

abp\_ack\_rc?b \rightarrow ABP\_TX(bit)

ATX(bit, v) = abp\_tx!(bit, v) \rightarrow ATX(bit, v)

abp\_ack\_rc?b \rightarrow (if (b = bit) then ABP\_TX(bit) else ATX(bit, v))

ABP\_RC = ABP\_RC(0)

ABP\_RC(bit) = abp\_rc?(b, x) \rightarrow (if (b = bit) then (app\_rc!x \rightarrow abp\_ack\_tx!b \rightarrow ABP\_RC(1-bit))

else (abp\_ack\_tx!b \rightarrow ABP\_RC(bit))

```

The transmission media and SYS cooperate according to

$$ABP = (M1 \parallel M1ACK) \parallel (ABP\_TX \parallel ABP\_RC)$$

To prove that ABP is an acceptable implementation of our ideal transmission medium, we have to show that

$$FIFO \sqsubseteq_{FD} ABP \setminus \{ | abp\_tx, abp\_rc, abp\_ack\_tx, abp\_ack\_rc | \}$$

which can be proven for finite maxLoss and buffer capacity N=1 using the FDR model checker.

Example 1.2 (Communication disturbed by insecure media) Let us now consider a transmission medium that is physically reliable but suffers from attacks by a malicious agent X. In the field of communication protocols, the most important types of attack have been classified as follows (see [9]): (1) Eavesdropping: Messages sent from PROD to CON are properly received by CON, but X can also receive (some of) them. (2) Blocking: X can receive messages intended for CON and prevent them from being delivered to CON.

(3) Delay: X can delay the transmission from PROD to CON. (4) Masquerading: X can send a fake message to CON that looks as if it has been sent by PROD. (5) Replay: X can send an old message that has already been sent from PROD to CON once more at a later point in time. (6) Tampering: X can alter a message while it is transmitted from PROD to CON, so CON receives modified data.

In this example, let the following behaviour be defined for the transmission medium:

- 1. **Security threat:** X can perform eavesdropping and tamper with data sent from PROD to CON. Making use of tampering, X can also replay a message by "copying" an old message onto a new package. X cannot block or delay messages or fake the identity of PROD. X can modify at most  $maxModified \geq 0$  messages in a row.

- 2. The medium delivers messages in the order of the corresponding inputs.

- 3. The medium does not lose messages.

- 4. While transmission of user data can be tampered with, there exists a separate reliable and secure communication channel for the transmission of control data.

The last condition may seem slightly artificial. I have added it in order to construct an extremely simple security protocol that works properly in this example but fails when combined with a fault-tolerance mechanism, as will be shown in the next example.

To defend the application layer against the insecure transmission medium M2 the architecture depicted in Figure 1.4 is chosen.

Figure 1.4: Security layer  $SEC1\_TX$ ,  $SEC1\_RC$  to protect the application layer against eavesdropping and tampering on M2 by agent X.

10 1. Introduction

The insecure behaviour of M2 may be modelled as follows:

```

\begin{split} M2 &= M2(maxModified) \\ M2(n) &= sec\_tx?x \rightarrow \\ & (\textbf{if } n = 0 \textbf{ then} \\ & (sec\_rc!x \rightarrow M2(maxModified)) \\ & \textbf{else} \\ & (sec\_rc!x \rightarrow M2(maxModified)) \\ & \sqcap \\ & sec\_rc!modify(x) \rightarrow M2(n-1))) \end{split}

```

Here output  $sec\_rc!modify(x)$  represents the case where X has tampered with input  $sec\_tx.x$ . Counter n prevents M2 from sending more than maxModified corrupted outputs in a row. M2ACK is assumed to be dependable and acts as a one-place buffer:

$$M2ACK = sec\_ack\_tx?b \rightarrow sec\_ack\_rc!b \rightarrow M2ACK$$

To meet the security threat represented by M2, the security layer implemented in SYS will use encryption techniques to detect altered or replayed messages and to prevent X from reading them. This technique will be explained in more detail in Chapter 2; for now it is sufficient that we may assume the existence of an encryption procedure  $\epsilon$  and an detection algorithm which signals isModified(x) = true if a package x has been tampered with. By  $\epsilon^-$  we denote the corresponding decoding procedure. The security layer may now be specified as

```

SEC1\_TX = app\_tx?x \rightarrow sec\_tx!\epsilon(x) \rightarrow S1TX(\epsilon(x))

S1TX(x) = sec\_ack\_rc.Modified \rightarrow sec\_tx!x \rightarrow S1TX(x)

\begin{bmatrix} \\ sec\_ack\_rc.Valid \rightarrow SEC1\_TX \end{bmatrix}

SEC1\_RC = sec\_rc?y \rightarrow

(\textbf{if } isModified(y))

\textbf{then } (sec\_ack\_tx!Modified \rightarrow SEC1\_RC))

\textbf{else } (app\_rc!\epsilon^-(y) \rightarrow sec\_ack\_tx!Valid \rightarrow SEC1\_RC)

```

Process  $SEC1\_TX$  accepts inputs from the application layer via channel  $app\_tx$ . It enciphers the message by means of  $\epsilon$  and passes the result to M2. As long as X does not know the key to decipher the message, it can only corrupt the data at random or copy an old package over the new data block. But this will be detected by  $SEC1\_RC$  using the isModified algorithm on the input y received on  $sec\_rc$ . If the message has been modified or is a replay of an old one,  $SEC1\_RC$  will send a control message Modified via M2ACK to  $SEC1\_TX$  and the latter will re-transmit the enciphered message. Since according to the assumptions neither M2 nor M2ACK lose messages and agent X can only modify, but not interrupt the communication on M2,  $SEC1\_TX$  can be sure to receive a response from  $SEC1\_RC$  for each message transmitted. It is therefore not necessary to watch for timeouts while waiting for the control

message. If the message has been received by  $SEC1\_RC$  without previous modification, the deciphered message contents will be passed on to CON, and control message Valid is sent back to  $SEC1\_TX$ . After that  $SEC1\_TX$  is ready to accept new data from PROD.

The complete secure implementation cooperates according to

```

SEC = (M2 \parallel M2ACK) \parallel (SEC1\_TX \parallel SEC1\_RC)

```

and again it may be shown using the FDR tool that

```

FIFO \sqsubseteq_{FD} SEC \setminus \{ | sec\_tx, sec\_rc, sec\_ack\_tx, sec\_ack\_rc | \}

```

for fixed values maxModified and buffer capacity N=1. The example does not show how to initiate communication and exchange keys for enciphering/deciphering between  $SEC1\_TX$  and  $SEC1\_RC$ . Possible solution for such identification, authentication and on-line key distribution procedures have been described in [9, 19].

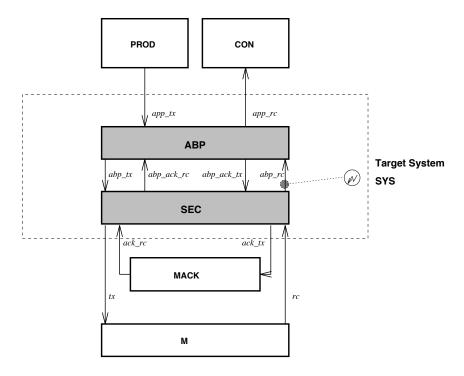

Example 1.3 (Naive combination of protocols in presence of more than one threat) Now what happens if we are confronted with a transmission medium M3 which is both unreliable in the sense of the first example and insecure in the sense of the second? It may be tempting to try and combine the existing solutions in an architecture as shown in Figure 1.5.  $SEC1\_TX$ ,  $SEC1\_RC$ , M2ACK are chosen as in the previous example.  $ABP1\_TX$ ,  $ABP1\_RC$  implement an alternating bit protocol on top of M3, M1ACK. They are copies of  $ABP\_TX/RC$  above, with channels  $app\_tx$ ,  $app\_rc$  renamed to  $sec\_tx$ ,  $sec\_rc$ . This seems to work at first sight, because the ABP layer makes up for lost messages and the security layer can deal with corrupted data.

We assume that M1ACK behaves as in Example 1, but M3 now combines the fault hypotheses and security threats of the previous examples according to

```

M3(n) = abp\_tx?(bit, x) \rightarrow

(\textbf{if } n = 0 \textbf{ then}

(abp\_rc!(bit, x) \rightarrow M3(maxModifiedOrLost))

else

(abp\_rc!(bit, x) \rightarrow M3(maxModifiedOrLost))

\sqcap

M3(n-1)

\sqcap

abp\_rc!(bit, modify(x)) \rightarrow M3(n-1)

\sqcap

abp\_rc!((1-bit), x) \rightarrow M3(n-1)

\sqcap

abp\_rc!((1-bit), modify(x)) \rightarrow M3(n-1)))

```

And this is the reason why this combination of mechanisms will fail: The resulting system will allow to block messages on  $app\_tx$  because

```

(M3 \parallel M1ACK) \parallel (ABP1\_TX \parallel ABP1\_RC) \parallel (SEC1\_TX \parallel SEC1\_RC) \\ \setminus \{ \mid sec\_tx, sec\_rc, sec\_ack\_tx, sec\_ack\_rc, abp\_tx, abp\_rc, abp\_ack\_tx, abp\_ack\_rc \mid \}

```

1. Introduction

Figure 1.5: Naive combination of security layer and network layer with unreliable and insecure medium M3. (For the sake of simplicity, M1ACK and M2ACK are assumed to be ideal transmission media.)

diverges: There exist traces of unbounded length consisting only of events other than  $app\_tx$ ,  $app\_rc$ . For example, consider the process DivTrace:

```

DivTrace = \\ app\_tx?x \rightarrow Div0(x)

Div0(x) = \\ sec\_tx.\epsilon(x) \rightarrow \\ abp\_tx.(0,\epsilon(x)) \rightarrow abp\_rc.(0, modify(\epsilon(x))) \rightarrow sec\_rc.modify(\epsilon(x)) \rightarrow \\ sec\_ack\_tx.Modified \rightarrow sec\_ack\_rc.Modified \rightarrow abp\_ack\_tx.0 \rightarrow \\ abp\_tx.(0,\epsilon(x)) \rightarrow abp\_rc.(0,\epsilon(x)) \rightarrow \\ abp\_ack\_rc.0 \rightarrow abp\_ack\_tx.0 \rightarrow abp\_ack\_rc.0 \rightarrow \\ sec\_tx.\epsilon(x) \rightarrow \\ abp\_tx.(1,\epsilon(x)) \rightarrow abp\_rc.(1, modify(\epsilon(x))) \rightarrow sec\_rc.modify(\epsilon(x)) \rightarrow \\ sec\_ack\_tx.Modified \rightarrow sec\_ack\_rc.Modified \rightarrow abp\_ack\_tx.0 \rightarrow \\ abp\_tx.(1,\epsilon(x)) \rightarrow abp\_rc.(1,\epsilon(x)) \rightarrow \\ abp\_ack\_rc.1 \rightarrow abp\_ack\_tx.1 \rightarrow abp\_ack\_rc.1 \rightarrow Div0(x)

```

DivTrace produces a trace which is correct with respect to the "naive system". This can be proven using FDR by checking that DivTrace is a correct trace refinement of

```

(M3 \parallel M1ACK) \parallel (ABP1\_TX \parallel ABP1\_RC) \parallel (SEC1\_TX \parallel SEC1\_RC)

```

presented.

The problem arises as follows: The message x sent by PROD via  $app\_tx$  is modified during the first transmission on M3, identified by bit '0'. As a consequence the control message  $sec\_ack\_tx.Modified$  is sent back to  $SEC1\_TX$ . Meanwhile a re-transmission is initiated by the ABP layer because the acknowledgement associated with the first message has not yet been received by  $ABP\_TX$ . This message passes M3 without any modifications, but it is useless, because  $ABP\_RC$  discards it on account of the same bit identification '0' as in the first transmission. Next  $ABP\_TX$  receives an acknowledgement for the first transmission, because is has been carried out successfully, as far as the ABP layer is concerned. Now the re-transmission  $sec\_tx.\epsilon(x)$  takes place, initiated by  $SEC\_TX$  as a response to the Modified control message. Again, this message is modified, this time carrying bit '1'. This procedure can be continued endlessly, and the hypothesis that at most maxModifiedOrLost consecutive messages may be corrupted is never violated, if maxModifiedOrLost > 0.

Note that it does not help to swap the ABP layer and the security layer: Since  $SEC1\_TX$  has been built under the assumption that messages will only be changed,  $SEC\_TX$  might wait forever for an acknowledgement on channel  $sec\_ack\_rc$  after a message has been lost on M3. This will prevent the ABP layer from re-transmitting the message.

In the next chapter, based on the systematic approach for the development of dependable systems, a correct protocol for the combined fault hypothesis and security threat will be

# 2. A Framework for the Development of Dependable Systems

#### 2.1 Overview

This chapter describes a formal approach for the systematic development of dependable systems. The necessity for such an approach is illustrated in Section 2.2 by means of an industrial project in the field of railway interlocking systems, which is a typical example of control systems requiring the full scale of dependability properties. Motivated by the introductory example presented in Section 1.2 we claim that any formal method suitable for the development of dependable systems should be applied according to a development standard (Section 2.3)<sup>1</sup>. Such a standard provides a re-usable framework for the specification and verification activities to be performed during the various phases of system development. It does not require a specific method to be applied but describes the activities to be performed and objects to be produced during the development stages. Tailored for the specific problems related to the development of dependable systems, it ensures that design errors as the one discussed in 1.2 are very unlikely to occur. Indeed, today many researchers and practitioners are convinced that a formal method can only be successfully applied in an industrial context if supported by both tools and a development standard.

The work presented in this chapter summarises and partly extends the results described in [78], using CSP [44] as the underlying method for the specification and verification of distributed systems. To overcome the problems specifically related to dependability in a systematic way, we make use of a method developed by Schepers [104] in the context of fault-tolerant systems. We will show in Section 2.4 how his method may be extended to the field of dependability in general, transforming the design obligation to develop a dependable system into the design obligation for an "ordinary" system. As for the development standard, we will focus on the *Vorgehensmodell (V-Model)* [112] which is authorised by the Germany Ministry of the Interior and considered as the state-of-the-art software development standard in Germany. Application of a standard helps to benefit from a formal method in the most systematic way during the software life cycle. Conversely, the formal approach will increase the insight about how the standard should be applied in an optimal way and what the documents informally introduced by the standard should describe to achieve a useful and reliable description of the system to be developed.

To illustrate the application of our approach, the case study of Chapter 1 will be re-worked in Section 2.5 in a systematic way, this time leading to a correct solution allowing to re-use at least one of the protocols introduced before to defend the system against isolated threats.

<sup>&</sup>lt;sup>1</sup>In this context "standard" means either an (inter-)national standard regulating development procedures or a "customised" company standard, which is usually an instantiation of an international or national standard for the specific type of tasks to be solved in the company.

## 2.2 Related Industrial Projects

The following example of a "real-world" project is presented to support the assertion that modern control systems should combine aspects of both "classical" dependability – i. e. safety, reliability, availability – and security. It has motivated the case study presented in Section 1.2, to be continued below. The example is typical for systems where classical dependability has always been an important issue, but the demand for security mechanisms is relatively new. Further examples are given in [78].

Distributed Railway Control System In Germany today, available electronic computer based railway control systems are centralised. One signal tower controls the state of all signals, points and level crossings of a specific area. Signals, points and level crossing barriers (or traffic lights) are directly wired to the signal tower. Each train is supervised by exactly one signal tower at a time. This technique is much too expensive for small private tramways, railway or underground networks. On the other hand, in the future these smaller networks will depend on highly automated control systems, because otherwise the operational costs would be too high. Therefore several European companies and research institutions investigate concepts for decentralised railway control.

Figure 2.1: System overview of a distributed interlocking system.

In one of these concepts<sup>2</sup> the control logic is distributed on a collection of 'local' switch boxes and on the trains (Figure 2.1). Each switch box controls a small number of nearby signals, points and level crossings. It stores its local system state, supervises its local safety conditions and communicates with approaching trains. The control computer of a train will request local state information from (several) switch boxes and decide, based on the state information available, whether signals, points and barriers or traffic lights may be switched according to the request of the train or whether the train will have to wait at a signal. Data between trains and switch boxes is communicated via radio transmission, preferably making use of standard networks designed for the purpose of digital data transfer.

<sup>&</sup>lt;sup>2</sup>The information in this paragraph is presented by courtesy of ELPRO LET GmbH. At present, I am working as a consultant for this company in the field of test automation and verification of components of interlocking systems. The concept is described in the proposal [26] in more detail.

This basic idea induces a variety of dependability requirements differing from those of centralised railway control system:

- The decision whether a train is allowed to pass a certain signal, point etc. is produced by a distributed algorithm which involves switch boxes "safe-guarding" their local safety requirements and the train control computer deducing the "global decision" from the local information of the switch boxes. The algorithm must never allow a transition into an unsafe state, even in the presence of component failures (safety requirement plus reliability requirement).

- Data exchange between trains and switch boxes has to apply protocols based on repreated package transmission to avoid the loss of data caused by accidental disturbance of the radio transmission (reliability requirement).

- The data transmission must also be protected against *systematic* manipulation by humans using radio transmission devices (security requirement).

Though the accidental physical disturbance of radio transmission will certainly be the threat with the highest probability, I believe that the idea of humans trying to manipulate the exchange of control signals does not represent a theoretical, but a very realistic threat. If hackers find it fascinating to plant viruses into other people's PCs (even though they cannot watch the effect in most cases), how much more fun would it be to stop, accelerate and re-direct a real train by "remote control", while watching the railway track! For these reasons, the distributed concept will introduce a new level of complexity. However, this does not represent an unmanageable problem, because the networks we consider here are much simpler structured and have a lower traffic rate than the big railways networks where the centralised concepts are used.

# 2.3 Standards for the Development of Dependable Systems

#### 2.3.1 Overview

Software Development Standards provide frameworks for the activities to be performed and objects to be produced during the software life cycle. They describe the logical links between development objects (specification documents, software code, test data etc.) and specify the activities to be exercised on the objects (development, review, verification etc.), as well as their "synchronisation" during the development life cycle. Ideally, the application of such a framework will help to meet the quality requirements applicable for the target system in the most systematic way. Standards admit a variety of methods – informal, semi-formal or formal – to be applied during the phases of system development. Therefore they are of informal nature themselves, written in natural language. However, they usually suggest the characteristics that should be present in a method, when applied to develop a system of certain criticality and according to pre-defined quality requirements. The relationship between standards, methods and tools is depicted in Figure 2.2.

Examples for standards with relevance in the field of dependable systems are

Figure 2.2: Relationship between standards, methods and tools.

- ISO 9000-3 [24] At present this is the most well known and at the same time the most general international standard providing rules with respect to organisational aspects of software projects and standardisation and documentation of the complete software development life cycle. Apart from rules concerning the process of software development itself, it emphasizes the regulation of *every* business process which may have a direct or indirect impact on the quality of software products developed in a company.

- ITSEC (Information Technology Security Evaluation Criteria) [47] This standard focuses on the security aspect of dependable systems. It will be discussed in more detail in Chapter 5.

- RTCA DO-178-B (Software Considerations in Airborne Systems and Equipment Certification) [22] The international development standard for software in civil aircrafts. Apart from the general requirements regarding project management, configuration management and software development, its main issues are the selection and justification of validation, verification and test methods, safety aspects and reliability aspects. The CIDS system [1] discussed in [85] has been developed according to this standard.

- V-Model ('Vorgehensmodell') [112] The standard for the development of software-based systems authorised by the German ministry of the interior.

Each of these standards is written in natural language. The objects and concepts used are informally defined and therefore subject to different interpretations. While each standard suggests the application of formal methods for the description and verification of the most critical system components, only few attempts have been made to show how the objects and concepts described in the standard should be related to the objects and concepts to be usually encountered when applying formal methods. With respect to the full scale of dependability issues, our approach to properly relate these different "worlds" appears to be a new enterprise. Similar investigations are currently carried out by Ravn and Stavridou [96, 97] with respect to the British Ministry of Defence Interim Standard MoD 00-55 [65]. In this chapter, we will discuss the regulations for software development according to the *V-Model*, because it may presently be regarded as one of the most advanced standards in Europe. Nevertheless, several

adjustments of the standard will be made concerning the structure and the contents of the documents introduced by the V-Model. These changes will be introduced in Section 2.3.2 and justified while introducing the formal approach in Section 2.4.

In Chapter 5 a similar approach will be described, this time focusing on security aspects only and referring to the ITSEC.

### 2.3.2 System Development According to the V-Model

#### **Process Model**

Similar to [24, 22], the *V-Model* adopts the well-accepted concept to model the whole system development procedure as a system of cooperating "meta" processes: Each team performs a well-defined task. In order to complete the task, inputs (documents, code, test data etc.) are received from the environment (e. g., the customer) and from other teams. After having processed the inputs, the corresponding outputs are distributed to the teams, to the customer and other external groups. The standard project structure comprises four cooperating processes: *Software Development Team, Project Management Team, Quality Assurance Team* and *Configuration Management Team*. In the following we will focus on the tasks to be performed by the software development and the quality assurance teams in the context of the development of dependable systems.

#### Levels of Abstraction

To make the development of large and complex systems more feasible, they are described by means of a collection of documents describing different levels of abstraction and associating a modular structure with each level. In the V-Model five levels of modularisation and abstraction are proposed for the full description of a system. They are informally introduced as (1) System Level: The top-level description of the whole target system without distinctions between software and hardware. Data and functions are described on the end user's level of abstraction. Interfaces to existing components in the environment (e.g., another computer) are described on the level of abstraction which is "seen" by the software to be developed for the target system. For example, if only application software has to be developed in a system layered according to the OSI model, the interface to an existing network is described on the level of abstraction offered by the send- and receive services provided by the OSI session layer for the application. (2) Sub-System Level: Large systems (e. g., a wide area network) may be decomposed into sub-systems (e.g., a local area network in the wide area network). in general without changing the level of abstraction for the representation of data, functions and interfaces. (3) Segment Level: This is a further modularisation step which partitions (sub-)systems into well-defined components (e. g. one computer in a network). On this level the segments consisting of hardware only are separated from those to be built out of both hardware and software. (4) SW Configuration Item Level: The software to be allocated in a segment is decomposed into different configuration items, each item representing a software sub-system (e.g., the processes associated with a specific layer of the OSI model which will be allocated in the segment). This is usually the starting point from where to change also the level of abstraction for the representation of data and associated functions. (5) Component Level: A part of a configuration unit, performing a well-defined service (e. g., one task of the configuration unit). Several component layers may be "inserted" to refine a top-level component (e. g., tasks might be decomposed into threads). (6) Module Level/Data Level: This is the lowest level of abstraction and modularisation to be distinguished according to the V-Model (e. g., a sequential function or a database table with associated attribute definitions).

#### Documents Associated With Each Level

The V-Model describes the documents to be associated with each level of abstraction and the topics to be covered by each document. In the context of this chapter two types of documents are of interest which appear (with slightly different naming and varying contents) on every level: (1) Requirements Description: This document type describes the functions, data and dynamic behaviour of an object associated with a specific level. In addition, boundary conditions restricting the class of possible realisations for the object are documented. (2) Architecture Description: This is a design structure which decomposes the object under consideration and/or refines its data structures. The process of decomposition introduces new objects to be associated with a lower level, as well as interfaces between them. Each new object is associated with its own lower-level requirements description. In this way, the alternation between requirements and architecture documents can be recursively applied to the decomposition tree from system to module level.

To illustrate the contents of requirements and architecture documents, let us look at the system level.

System Requirements The system requirements document should describe what the system is supposed to do without telling us how this can be achieved. Specifically, the document describes the following aspects: (1) Operational Environment: The external interfaces and hypotheses about the normal behaviour of the environment. (2) Application Requirements: A specification of the functions, data and dynamic behaviour of the complete application, as seen by the end user. The application requirements describe this behaviour in relation to the operational environment (1). This means that other types of behaviour have to be expected, if the characteristics of the operational environment are changed. (3) Threat Analysis (External): A specification of those possible deviations from normal behaviour which are to be expected in the environment (e.g., crash of external computers, security attacks by unauthorised users from outside the system, corrupted data at an input interface). For each threat the list of dependability requirements it might impair is documented. Note that since at this stage nothing is known about the *internal* structure of the system, only external threats can be specified. (4) Dependability Requirements: A list associating items from the application requirements with safety, reliability/availability and security requirements. This describes the degree of protection to be established for each of these items in case of a deviation of the environment from normal behaviour. (5) Risk Analysis (External): An estimator associated with each threat, specifying the probability for the corresponding exceptional behaviour to occur.

This is not the complete list of items to be covered by the system requirements document, but the others described in [112] are not relevant in our context. It is more important to note that we have deviated from the description [112] in the following ways:

• According to the *V-Model*, security requirements and reliability requirements are de-

scribed in different parts of the document, while safety requirements are subsumed under reliability and availability is not mentioned at all. I think that this is inappropriate, since it will be illustrated below that all dependability aspects can be covered by a unified approach. Therefore I have decided to introduce the general term *Dependability Requirements* where safety, reliability, availability and security issues should be described.

• The *V-Model* does not distinguish between external and internal threat/risk analysis. I regard this as an important aspect, because in general designers will have no influence on external threats, while they can influence the internal ones by means of their design decisions.

System Architecture The main topics to be covered by the system architecture document are (1) System Structure: The system is decomposed into sub-systems, segments or software configuration items. (2) External Interfaces: The external interfaces described in the system requirements document are allocated to the corresponding components of the system structure. (3) Internal Interfaces: The internal communication paths between the new components are defined. This gives rise to interface specifications for the requirements documents associated with each component using the interface. (4) Requirements Allocation: Each application requirement is associated with one or more components of the system structure which have been designed to implement the requirement. This induces application requirements specifications for each component. (5) Dependability Requirements Allocation: The dependability requirements are mapped to corresponding components designed in the system structure. This induces dependability requirements for each of these components. (6) Threat Analysis (Internal): The decomposition introduces new interfaces and new components, therefore new threats may arise in addition to the external threats (e.g., component failure, security leak inside the system). (7) Risk Analysis (Internal): associated with the internal threat analysis. (8) Dependability Concept: It is explained how the system dependability requirements can be achieved by means of the chosen system structure in combination with the requirements defined for each component.

Here we have altered the suggestions of the V-Model in the following way:

- In [112] only the description of the security concept is required. Consistent with the change proposed for the system requirements, we will describe the complete dependability concept instead.

- The internal threat/risk analysis is missing in the *V-Model*. This also holds for the requirements and architecture documents associated with the lower levels of description. This seems to be an important aspect overlooked by the authors of [112]: Each design decision may introduce new threats to the dependability requirements. Therefore it is necessary to perform a new threat analysis at each level of decomposition.

# 2.4 A Formal Approach for the Development of Dependable Systems

#### 2.4.1 Selection Criteria for the Formal Method

When choosing a suitable formal method for the development of dependable systems of the type introduced in the case study in Chapter 1, the following selection criteria have been considered:

- Specification of distributed systems: Since the problem belongs to the field of distributed systems, the underlying method should allow to specify aspects of concurrency, synchronisation etc. in a suitable way.

- Compositional and modular refinement: The technique of describing the target system by means of stepwise decomposition, as suggested by the V-model, is related to refinement in a natural way. Moreover, there are two types of refinement that typically occur during the development process. They have been explored in detail by Zwiers [120]: If the designer has full freedom in the decomposition of a system component, being allowed to choose both the architecture and the specifications of the lower-level components created in the decomposition step, we speak of compositional refinement. If, on the other hand, existing components (e. g., off-the-shelf software) have to be used in the decomposition step we are confronted with pre-defined specifications and have to adjust the architecture and the specifications of new modules in such a way that the pre-defined ones can be integrated. This situation is called modular refinement. Since most software projects require both the development of new components and the integration of existing ones, we require that a suitable method should allow both compositional and modular refinement.

- **Dependability features:** The formal method should allow to derive systematically the description of system behaviour in presence of (combinations of) threats.