# An Evolutionary Approach to Reconfigurable Scan Network Design

Payam Habiby<sup>†</sup>

Fatemeh Shirinzadeh<sup>†</sup>

Rolf Drechsler\*<sup>†</sup>

\*University of Bremen, Germany {habiby,shirinfa,drechsler}@uni-bremen.de <sup>†</sup>Cyber-Physical Systems, DFKI GmbH 28359 Bremen, Germany

*Abstract*—The IEEE Std. 1687 (IJTAG) provides an efficient methodology for accessing instruments in complex integrated circuits through reconfigurable scan networks. Despite significant improvement provided by this method in accessing instruments, designing an optimized network that meets a set of non-functional constraints, and minimizes the overall access time, routing, and area overhead is a non-trivial optimization problem. This paper tackles this challenge by proposing an evolutionary approach to synthesize reconfigurable scan networks with optimized routing and area overhead while minimizing the overall test time.

## I. INTRODUCTION

IEEE Std. 1687 (IJTAG) enables the reduction of overall access time in complex integrated circuits through reconfigurable scan networks [1]. However, incorporation of programmable elements necessitates a deliberate network design methodology to maintain an optimized performance of the scan networks. The previous efforts for optimizing the access mechanism either require the modification of the standard IJTAG components or only consider a single-objective design approach [2]-[4]. However, the proposed method develops an evolutionary multiobjective optimization approach to design IJTAG networks. In addition, the proposed method adheres to IEEE Std. 1687 design rules and therefore doesn't necessitate the introduction of new components or modifications of the standard IJTAG elements. The main contribution of this work is the simultaneous minimization of routing and area overhead while reducing the overall access time.

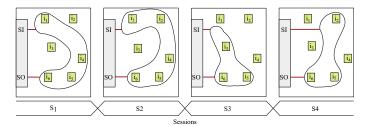

Fig. 1 explains the IJTAG network design problem for a chip comprising six instruments with given power consumption and specified number of required instruments' read/write cycles. According to a calculated schedule, four scan sessions are defined to test all instruments. Every session requires its own configured scan chain that provides access to the scheduled subset of instruments. The sequence of instruments between SI and SO on the scan chain in each session and also the location of the branching and merging points of scan chains to form a network are unknown. These factors significantly affect the number of synthesized ScanMuxes, time, and routing overhead of the scan network. The proposed method tackles the challenge of network design by formulating it as a multiobjective evolutionary optimization problem.

#### II. PROPOSED SCAN NETWORK DESIGN METHODOLOGY

As discussed in [4]–[6], an IJTAG network can be modeled as a *Directed Acyclic Graph* (DAG) which can be represented

Fig. 1: Scheduled test sessions for designing an IJTAG network with minimized test time, routing, and flip-flop overhead.

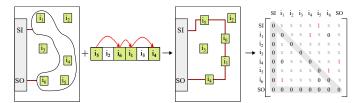

by an adjacency matrix. A permutation-based evolutionary approach is taken to design such a network graph by generating this matrix as a phenotype and calculating the fitness function for finding the best solution. At initial step, a scheduler is employed to calculate a test schedule that provides a minimized overall access time while adhering to the specified power and access constraints [5]-[7]. Next, every instrument is regarded as a gene and thereby the sequence of all instruments constitutes a genotype. Changing the sequence of instruments results in a new genotype, consequently forming the permutation search space from all potential gene combinations. Every genotype is in fact a topological order of the nodes in the network graph. Applying this order to the scheduled test sessions enables the generation of a unique phenotype in form of a network adjacency matrix as described in Fig. 2. In this figure, the scheduled session implies serial access to the instrument set  $\{i_6, i_4, i_1, i_5\}$  starting from SI and leading to SO port. Following the sequence of genes in the genotype, the instruments of the scheduled session are arranged to form the scan chain  $\{i_5 \rightarrow i_6 \rightarrow i_1 \rightarrow i_4\}$ . Subsequently, the related elements of the adjacency matrix are modified to represent the graph edges. By applying the same genotype to the remaining sessions of the schedule, other elements of the matrix are populated. Having the matrix constructed, the objective and fitness functions are calculated according to equations 1 to 5.

Objective Functions: Assuming M as an  $n \times n$  adjacency matrix of the desired graph, the Boolean decision variable  $x_{ij}$  decides if a directed edge  $e_{ij}$  exists between the instruments i and j, where n denotes the number of instruments. The first objective functions addresses the routing overhead by minimizing the number of edges of the network graph:

$$f_1 = Min \sum_{i,j=0}^{n} x_{ij} \qquad x \in \mathbb{B}$$

(1)

Fig. 2: Extracting the scan chain and graph matrix based on the genotype for a test session.

The second objective is minimizing the area overhead introduced by generated configuration flip-flops. This is equal to the number of select inputs of the multiplexers created at merging nodes of the network graph:

$$F = \lceil \log_2(\sum_{i=0}^n x_i) \rceil \qquad x \in \mathbb{B}.$$

(2)

Now, the second optimization objective is obtained by minimizing the sum of flip-flops over all columns of adjacency matrix:

$$f_2 = Min \sum_{j=0}^n F_j \qquad F \in \mathbb{W}.$$

(3)

*Fitness Function:* The weighted sum method is employed to approximate the multi-objective problem using a single-objective model. This approach provides designers with the flexibility to prioritize either routing or area overhead by introducing weights. The equations 1 and 3 are combined as follows to form a single fitness function:

1

$$\mathcal{F} = \frac{\iota}{\omega_1 \times f_1(x) + \omega_2 \times f_2(x)} \qquad \qquad \begin{array}{l} \omega_1, \omega_2 \le 1 \\ \omega_1 + \omega_2 = 1 \end{array}$$

(4)

Where  $\omega_1$  and  $\omega_2$  indicate the arbitrary weights of the initial objective functions and l is a scale factor. Finally, the optimization problem is defined as finding a graph that maximizes the fitness function:

$$Max\{\mathcal{F}\}.$$

(5)

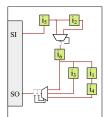

For creating the offspring, *order crossover operator* (OX1) [8], and *swap mutation* are used. The new individuals produced by the evolutionary operators create a population. A subset of this population with the highest fitness value are selected as elites to survive and persist to the next generation. This prevents quality degradation of the future generations by preserving high quality individuals. After exploring the search space using the introduced operators, and evaluating every individual using the proposed fitness function, the fittest solution is selected as the best topological order. Subsequently, this order is utilized in conjunction with the calculated schedule to generate the optimized scan network graph like the example shown in Fig. 3

### **III. EVALUATION AND CONCLUSION**

In order to evaluate the proposed design method, ITC'16 benchmark networks have been re-synthesized [9]. The experimental results are compared with the synthesized networks reported in [4] since the method of this work is compatible with multi-power domain SoCs, and follows the IJTAG design paradigms without introducing structural modifications to the standard scan elements. Table I shows that for all benchmark

Fig. 3: The synthesized IJTAG network based on the given schedule of Fig. 1.

TABLE I: Comparing the generated IJTAG network with [4]

| Network    | Configuration flip-flops |          | Routing overhead |          | Access time overhead [clk] |           |

|------------|--------------------------|----------|------------------|----------|----------------------------|-----------|

|            | [4]                      | Proposed | [4]              | Proposed | [4]                        | Proposed  |

| Mingle     | 9                        | 6        | 21               | 16       | 197                        | 173       |

| TreeFlat   | 15                       | 10       | 30               | 23       | 280                        | 230       |

| q12710     | 27                       | 23       | 64               | 54       | 854                        | 762       |

| t512505    | 307                      | 299      | 718              | 702      | 35,929                     | 35,009    |

| p22810     | 647                      | 636      | 1,535            | 1,518    | 138,080                    | 135,748   |

| p34392     | 135                      | 132      | 295              | 285      | 9,193                      | 8,998     |

| N17D3      | 29                       | 26       | 72               | 64       | 1,351                      | 1,276     |

| N32D6      | 70                       | 66       | 155              | 140      | 3215                       | 3051      |

| N73D14     | 193                      | 186      | 444              | 398      | 17,801                     | 17,185    |

| N132D4     | 389                      | 387      | 930              | 920      | 63,590                     | 63,272    |

| NE1200P430 | 5,213                    | 5,200    | 15,285           | 15,231   | 7,464,753                  | 7,446,163 |

networks, the proposed methodology optimizes all three design objectives, namely area and routing cost, as well as the overall access time overhead. In the end, this paper proposed a multi-objective evolutionary approach to synthesize power-safe reconfigurable scan networks for multi-power domain SoCs. According to the experimental results the proposed approach is scalable and provides an optimized topology of reconfigurable scan networks.

#### References

- [1] "IEEE standard for access and control of instrumentation embedded within a semiconductor device," *IEEE Std. 1687-2014*, pp. 1–283, 2014.

- [2] S. Gupta, A. Crouch, J. Dworak, and D. Engels, "Increasing IJTAG bandwidth and managing security through parallel locking-SIBs," in *IEEE International Test Conference*, 2017, pp. 1–10.

- [3] M. A. Ansari, J. Jung, D. Kim, and S. Park, "Time-multiplexed IEEE 1687network for test cost reduction," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, vol. 37, no. 8, pp. 1681–1691, 2018.

- [4] P. Habiby, N. Lylina, C.-H. Wang, H.-J. Wunderlich, S. Huhn, and R. Drechsler, "Synthesis of IJTAG networks for multi-power domain systems on chips," in 2023 IEEE European Test Symposium (ETS), 2023, pp. 1–6.

- [5] P. Habiby, S. Huhn, and R. Drechsler, "Power-aware test scheduling for IEEE 1687 networks with multiple power domains," in *IEEE International Symposium on Defect and Fault Tolerance in VLSI and Nanotechnology Systems*, 2020, pp. 1–6.

- [6] P. Habiby, S. Huhn, and R. Drechsler, "Power-aware test scheduling framework for IEEE 1687 multi-power domain networks using formal techniques," *Microelectronics Reliability*, vol. 134, p. 114551, 2022.

- [7] P. Habiby, S. Huhn, and R. Drechsler, "Optimization-based test scheduling for IEEE 1687 multi-power domain networks using Boolean satisfiability," in *International Conference on Design Technology of Integrated Systems* in Nanoscale Era, 2021, pp. 1–4.

- [8] D. Lawrence, Handbook of genetic algorithms. Van Nostrand Reinhold, 1991.

- [9] "IEEE 1687 Std. benchmark networks," 2016. [Online]. Available: https://gitlab.com/IJTAG/benchmarks