Nr. 18 | Wintersemester 2018/2019

Liebe Leserinnen

und Leser,

Liebe Leserinnen

und Leser,

obwohl der Sommer - auch hier in Bremen - ungewöhnlich sonnig war, haben wir dennoch eine Menge wissenschaftliche Ergebnisse und Erfolge vorzuweisen, die wir Ihnen im Folgenden präsentieren. Ganz besonders wollen wir dabei auf die Entwicklung eines SystemC-basierten RISC-V Virtuellen Prototyps hinweisen, den wir quelloffen zur Verfügung stellen. Darüber hinaus berichten wir über vielfältige internationale Aktivitäten und über die neuesten Entwicklungen in zwei von der DFG geförderten Sonderforschungsbereichen. Neben unseren Forschungsarbeiten sind wir auch wieder in einer Schule aktiv gewesen, um Interesse für Informatik zu wecken - auch darüber berichten wir.

Ich wünsche Ihnen eine inspirierende Lektüre

und einen guten Start ins Wintersemester!

Erster Open Source RISC-V Virtueller Prototyp

Erster Open Source RISC-V Virtueller PrototypIm Rahmen der Vorlesung "Praktische Einführung in den modernen Systementwurf mit C++" entstand die Idee, einen top-aktuellen Virtuellen Prototypen eines Prozessors

zu modellieren. Die Wahl der Befehlssatzarchitektur (Instruction Set Architecture, ISA) war schnell getroffen: RISC-V. RISC-V wurde von der University of California in

Berkeley unter der Leitung von Krste Asanovic und David A. Patterson zusammen mit Industriepartnern entwickelt. Da es sich bei RISC-V um eine quelloffene und lizenzfreie

ISA handelt, können selbstentwickelte RISC-V-Prozessoren ohne die Zahlung von Lizenzgebühren verkauft werden. Diese und viele weitere Vorteile machen RISC-V für die

Forschung und Industrie sehr attraktiv.

Auf Grund der langjährigen Expertise im Bereich SystemC-basierter Virtueller Prototypen (VP) gelang es, den ersten SystemC-basierten RISC-V VP zu entwickeln. Ganz im

Sinne der RISC-V Foundation, welche die Spezifikationen der RISC-V ISA koordiniert, stellen wir unseren RISC-V VP quelloffen unter MIT-Lizenz zur Verfügung. Im September

präsentierte Vladimir Herdt in seinem Vortrag "Extensible and Configurable RISC-V based Virtual Prototype"

unseren RISC-V VP auf dem Forum on specification & Design Languages (FDL) in München einer breiten Fachcommunity. Darüber hinaus entstehen gerade im Rahmen des BMBF

Projektes CONFIRM gemeinsame Erweiterungen und Optimierungen am VP. Forschungsfragen rund um den Firmware-basierten Entwurf werden wir in dem von Daniel Große

organisierten Tutorial "Firmware Firmly under Control: New Optimization and Verification Techniques for Application Specific Electronic Systems" auf der Design and

Verification Conference and Exhibition Europe (DVCon Europe) erörtern und beantworten.

Github Links zu unseren RISC-V Projekten unter: www.systemc-verification.org/riscv-vp.

Verifikation von arithmetischen Schaltkreisen

Verifikation von arithmetischen SchaltkreisenArithmetische Schaltkreise haben eine sehr hohe praktische Relevanz, da diese in jedem Prozessor, IoT-Geräten, aber auch aufkommenden Hardwarearchitekturen im Bereich Künstlicher Intelligenz zu finden sind. Dabei ist ihre funktionale Korrektheit unabdingbar, da fehlerhafte Chips zu enorm hohen Kosten führen. Die Arbeit von Alireza Mahzoon, Daniel Große und Rolf Drechsler mit dem Titel "Combining Symbolic Computer Algebra and Boolean Satisfiability for Automatic Debugging and Fixing of Complex Multipliers", die beim IEEE Computer Society Annual Symposium on VLSI (ISVLSI) im Juli in Hong Kong vorgestellt wurde, adressiert die Verifikation und das Debugging von arithmetischen Schaltkreisen. Der Fokus liegt dabei insbesondere auf Multiplizierern, deren Korrektheit bislang nur für recht kleine Bitbreiten vollautomatisch nachgewiesen werden kann. Die in der Arbeit vorgestellten Ergebnisse erlauben es erstmalig, Fehler in komplexen Multiplizierern zu lokalisieren und zu beheben.

ETS 2018

ETS 2018Vom 28. Mai bis 01. Juni 2018 fand im Swissôtel in Bremen das 23. IEEE European Test Symposium (ETS 2018) statt. Zu den Sponsoren dieser

Tagung gehörten neben der Deutschen Forschungsgemeinschaft (DFG) auch Intel, Infineon, Qualcomm, Mentor, Ridgetop, Advantest, Cadence und Bosch.

Zu dieser international bedeutenden Konferenz für den Test von elektronischen Schaltkreisen und Systemen waren über 200 Teilnehmerinnen und Teilnehmer aus Wissenschaft

und Industrie angereist. Eine Vielzahl von Vorträgen befasste sich mit neuen Ideen und Trends im Bereich Test und Zuverlässigkeit elektronischer Schaltkreise

und Systeme. Thematisch ging es um den Test von sowohl digitalen als auch analogen Schaltungen, dabei lag auch ein Schwerpunkt auf Möglichkeiten der Verbesserung der

Testbarkeit sowie auf der Reduzierung von Kosten.

In Verbindung mit dem ETS fand zudem die dreitägige Test Spring School (TSS) vom 25. bis 28. Mai 2018 im Schloss Etelsen in Langwedel statt. Die Test Spring School

richtet sich insbesondere an Nachwuchswissenschaftlerinnen und -wissenschaftler. Inhaltlich lag in diesem Jahr ein Schwerpunkt auf der Sicherheit von Hardware und auf

Herausforderungen moderner Sicherheitstechnologien.

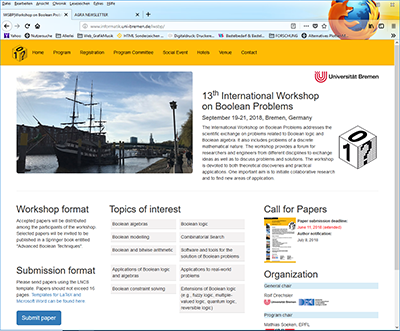

IWSBP 2018

IWSBP 2018Ebenfalls in Bremen wurde vom 19. bis 21. September 2018 der 13. International Workshop on Boolean Problems (IWSBP 2018) ausgerichtet (General Chair: Rolf Drechsler, Program Chair: Mathias Soeken, EPFL Lausanne, Schweiz). Dieser internationale Workshop ermöglicht einen wissenschaftlichen Austausch im Bereich Boolescher Logik und Boolescher Algebra sowie zu Problemstellungen mit diskreten mathematischen Eigenschaften. Neben einer Vielzahl von Beiträgen waren auch die Keynotes unserer ehemaligen Kollegen Prof. Görschwin Fey (TUHH Hamburg) und Prof. Tim Güneysu (Ruhr-Universität Bochum) Höhepunkte des Workshops.

Erfolgreiche Zusammenarbeit mit Wissenschaftlern aus dem Bereich der Elektrotechnik

Erfolgreiche Zusammenarbeit mit Wissenschaftlern aus dem Bereich der ElektrotechnikMit einem Beitrag beim 24. IEEE International Symposium on On-Line Testing and Robust System Design (IOLTS) beginnt Rehab Massoud eine erfolgversprechende Zusammenarbeit mit der Elektrotechnik. Gemeinsam mit Jaan Raik (Tallinn University of Technology), Robert Schmidt und Alberto Garcia-Ortiz (Universität Bremen) entstand die Arbeit mit dem Titel "Reliability Improvements for Multiprocessor Systems by Health-Aware Task Scheduling", die im Juli in Platja d'Aro, Costa Brava, Spanien vorgestellt wurde.

Klausurtagung des Sonderforschungsbereiches "Farbige Zustände"

Klausurtagung des Sonderforschungsbereiches "Farbige Zustände"

Am 11. und 12. September fand die Klausurtagung des von der DFG geförderten Sonderforschungsbereiches 1232 "Von farbigen Zuständen zu evolutionären Konstruktionswerkstoffen"

im Seminarhotel Kunze-Hof in Stadtland am Jadebusen statt. Auf dieser zweitägigen Veranstaltung wurden die vielfältigen Ergebnisse der einzelnen Teilprojekte präsentiert,

die seit Beginn im Juni 2016 erarbeitet wurden und bereits erste vielversprechende Erkenntnisse gezeigt haben.

Wesentlicher Bestandteil dieser Tagung war zudem die strategische Ausrichtung für die nächste Förderphase: Ein Sonderforschungsbereich besteht aus insgesamt drei

vierjährigen Förderphasen, die jeweils nach dem vierten bzw. achten Jahr umfangreich evaluiert werden. Bei positiver Evaluation beginnt die zweite Phase im Juli 2020.

Klausurtagung des Sonderforschungsbereiches "Everyday Activity Science and Engineering"

Klausurtagung des Sonderforschungsbereiches "Everyday Activity Science and Engineering"Der Sonderforschungsbereich 1320 "Everyday Activity Science and Engineering" (EASE) traf sich am 27. und 28. September in Walsrode zu einer Klausurtagung. Es wurden interessante Ergebnisse der einzelnen Teilprojekte dargestellt und diskutiert. In diesem interdisziplinären SFB wird seit Sommer 2017 daran gearbeitet, dass Roboter abstrakte Anweisungen selbständig umsetzen können. Insgesamt gliedert sich der SFB in drei Forschungsbereiche, die das Thema Alltagsaktivitäten unter einem jeweils spezifischen Aspekt untersuchen: Im ersten Bereich (Descriptive models of human everyday activity) entwickeln die EASE-Forschenden unter anderem mit den Methoden der Neuropsychologie, Neuroinformatik und Linguistik neue Modelle für die Beschreibung menschlicher Alltagsaktivitäten. Der zweite Bereich (Principles of information processing for everyday activity) untersucht unter anderem mit den Mitteln der Theoretischen Informatik neue Methoden für Wissensrepräsentation und automatisches Schlussfolgern für Alltagsaktivitäten. Im dritten Forschungsbereich (Generative models for mastering everyday activity and their embodiment) werden die Erkenntnisse aus den beiden anderen Bereichen auf Robotersysteme übertragen und getestet. Unsere Arbeitsgruppe ist im zweiten Forschungsbereich beteiligt und erforscht die Formalisierung und Verifikation von Plänen.

Im vergangenen Semester besuchten uns die folgenden Wissenschaftlerinnen und Wissenschaftler und bereicherten unsere Arbeit durch interessante und inspirierende Diskussionen:

- Dr.-Ing. Shahin Tajik, TU Berlin, 24.04.

- Karsten Einwich und Thilo Vörtler, Coseda Technologies GmbH Dresden, 13.-14.08.

- Prof. Dr. Roland Meyer, Prakash Saivasan (PhD) und Peter Chini, TU Braunschweig, 13.-14.09.

Wintersemester 2018/2019

03-BB-701.01

04-V07-B-001

03-BP-902.61

03-MP-902.56

Abschlussarbeiten

Abschlussarbeiten stellen den Höhepunkt des Studiums dar. In der Arbeitsgruppe kann dabei eine Vielzahl an verschiedenen Themen bearbeitet werden. An dieser Stelle präsentieren wir die Abschlussarbeiten, die im letzten Semester in unserer Gruppe abgeschlossen wurden.

- Jan von Bargen, Heuristisches IDS zur präventiven Detektion von rowhammer-typischen Systemangriffen, Bachelor, 2018

- Rune Krauss, Effiziente Implementierung von Binären Entscheidungsdiagrammen, Bachelor, 2018

- Mert Arat, Robustheit von konvolutionalen neuronalen Netzen für Bilderkennung im Automotive Bereich, Bachelor, 2018

Du hast Interesse, deine Abschlussarbeit in der Arbeitsgruppe Rechnerarchitektur anzufertigen?

Dann melde dich

einfach bei uns: drechsler@uni-bremen.de.

Erfolgreiche Verteidigung der Dissertation

Erfolgreiche Verteidigung der Dissertation

Herr Dr. Zaid Saleem Ali Al-Wardi hat am 23.04.2018 seine Dissertation mit dem Titel "HDL-based Synthesis of Reversible Circuits - A Scalable Design Approach" erfolgreich

verteidigt. Reversible Schaltungen zählen zu einer neu aufkommenden Form von Schaltungen, bei denen man Berechnungen nicht nur von den Eingängen zu den Ausgängen durchführen

kann, sondern auch in die andere Richtung. Damit unterscheiden sie sich deutlich von konventionellen Schaltungen, bei denen man z.B. aus einer Summe nicht eindeutig auf die

entsprechenden Summanden schließen kann. Für Anwendungen im Bereich des Quantum Computing oder des Low-Power Design sind solche Schaltungen sehr interessant;

allerdings gibt

es bislang nur wenige Hardwarebeschreibungssprachen für die Implementierung dieser Schaltungen. Zudem liefern diese oft noch unbefriedigende Ergebnisse. Im Rahmen

seiner Dissertation hat sich Dr. Zaid Saleem Ali Al-Wardi intensiv damit beschäftigt, wie man mit Hilfe von Hochsprachen effiziente reversible Schaltungen entwerfen und

schließlich synthetisieren kann.

Zur Promotion gratulieren wir sehr herzlich und wünschen weiterhin viel Erfolg!

Dr. Oliver Keszöcze an Friedrich-Alexander-Universität Erlangen-Nürnberg (FAU) berufen

Dr. Oliver Keszöcze an Friedrich-Alexander-Universität Erlangen-Nürnberg (FAU) berufen

Zum 1. September 2018 folgte Dr. Oliver Keszöcze einem Ruf auf eine Juniorprofessur an die Friedrich-Alexander-Universität Erlangen-Nürnberg (FAU). Inhaltlich wird er

dort zum einen seine Forschungsarbeit auf dem Gebiet der Biochips vorantreiben, zum anderen wird er sich verstärkt mit dem Thema des "Approximate Computing" befassen.

Oliver Keszöcze war seit 2012 Mitglied unserer Arbeitsgruppe und schloss im Juni 2017 erfolgreich seine Promotion zum Thema "Exact Design of Digital Microfluidic Biochips"

ab. Seine Errungenschaften auf dem Gebiet des Designs Mikrofluidischer Biochips wurden im März dieses Jahres im Rahmen des Doktorandenforums auf der Konferenz "Design,

Automation and Test in Europe" (DATE 2018) in Dresden mit dem "Best Poster Prize" gewürdigt.

Wir gratulieren sehr herzlich und wünschen weiterhin Alles Gute!

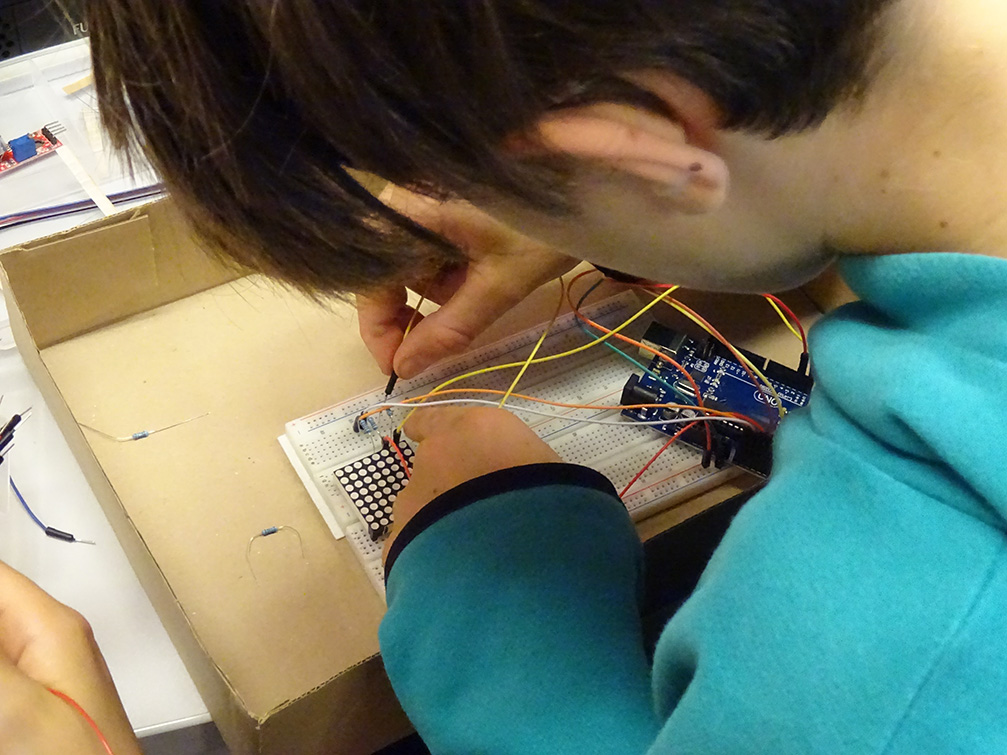

Zum zweiten Mal: Arduinos in der Schule

Zum zweiten Mal: Arduinos in der Schule

In einer Kooperation des von der DFG geförderten Sonderforschungsbereichs 1232 "Farbige Zustände" mit der Wilhelm-Focke-Oberschule in Bremen arbeiteten wir nun zum

zweiten Mal mit "unserer" Klasse zusammen. Nachdem ein erstes Modul im vergangenen Schuljahr ein großer Erfolg war, programmierten wir auch in diesem Schuljahr wieder

Mikrocontroller - wobei das primäre Ziel nicht darin besteht, Kenntnisse in C/C++ zu vermitteln, sondern generelles Interesse an Technik und Informatik zu fördern.

Unsere Sechstklässler waren hochmotiviert dabei, mit Arduino-Unterstützung die Klassenkameraden bei dem Spiel "Schiffe versenken" zu schlagen…

Erkenntnisse aus dieser Kooperation wurden in einer Arbeit mit dem Titel "Arduinos in der Schule - Lernen mit Mikrocontrollern" in der Zeitschrift "Computer +

Unterricht" publiziert. Weitere Informationen finden Sie hier.

Foto: Claudia Sobich / SFB 1232

| Kontakt: | Sebastian Huhn | E-Mail: huhn@informatik.uni-bremen.de |

| Cornelia Große | E-Mail: cornelia.grosse@uni-bremen.de |

Internationale Aktivitäten

Internationale Aktivitäten

Im Sommer waren wir auf einigen internationalen Tagungen vertreten. So reisten Oliver Keszöcze, Alireza Mahzoon und Saeideh Shirinzadeh nach Hong Kong

zum IEEE Computer Society Annual Symposium on VLSI (ISVLSI) und präsentierten dort Arbeiten zu "Logic Synthesis for In-Memory Computing using Resistive

Memories", "Combining Symbolic Computer Algebra and Boolean Satisfiability for Automatic Debugging and Fixing of Complex Multipliers", sowie "Towards

Dynamic Execution Environment for System Security Protection against Hardware Flaws". Oliver Keszöcze und Frank Sill Torres reisten zur Euromicro Conference

on Digital System Design (DSD) nach Prag; Oliver Keszöcze leitete dort eine Special Session zum Thema "Future Trends in Emerging Technologies", Frank Sill

Torres präsentierte die Arbeiten "Exploration of the Synchronization Constraint in Quantum-dot Cellular Automata" und "Evaluating the Impact of

Interconnections in Quantum-Dot Cellular Automata".

Rolf Drechsler ist Mitglied im "Externen Ständigen Beirat für die Durchführung von Tenure Track-Verfahren"

Rolf Drechsler ist Mitglied im "Externen Ständigen Beirat für die Durchführung von Tenure Track-Verfahren"

Rolf Drechsler wurde als Mitglied im "Externen Ständigen Beirat für die Durchführung von Tenure Track-Verfahren" an der Goethe-Universität in Frankfurt

am Main ernannt. Das erste Treffen dieses Externen Beirats fand am 08. Mai in Frankfurt statt. Als Mitglied des Externen Beirats unterstützt Rolf Drechsler -

gemeinsam mit drei weiteren Professoren aus den Bereichen Gesellschaftswissenschaften (Prof. Dr. Georg Götz), Geisteswissenschaften (Prof. Dr. Andreas Speer)

und Lebenswissenschaften (Prof. Dr. Kirsten Jung) - die Goethe-Universität bei der Berufung und Evaluation von Professorinnen und Professoren mit Tenure Track.

Best Poster Award für Buse Ustaoglu

Best Poster Award für Buse Ustaoglu

Für ihre Arbeit "SAT-Lancer: A Hardware SAT-Solver for Self-Verification", die Buse Ustaoglu im Mai beim 28th ACM Great Lakes Symposium on VLSI (GLVLSI) in

Chicago vorstellte, erhielt sie den "Best Poster Award". Thematisch ist die Arbeit im Bereich des Nachweises der Korrektheit von elektronischen Geräten

angesiedelt. In der Arbeit wurde auf das fundamental neue Konzept der Selbstverifikation gesetzt. Dies bedeutet, dass sich Systeme während des Betriebs

selbst verifizieren. Zur praktischen Umsetzung der Selbstverifikation müssen die Verifikationskomponenten jedoch vollständig in Hardware realisiert werden.

Eine solche Verifikationskomponente mit dem Namen SAT-Lancer wurde in dem Paper vorgestellt. Diese erlaubt es, vollständig in Hardware zu prüfen, ob eine

Menge von logischen Formeln, eine sogenannte SAT-Instanz, eine Lösung besitzt oder eben nicht. Die zentrale Herausforderung bei der Entwicklung von SAT-Lancer

war es, ein skalierbares Speichermodell zu entwickeln, um die logischen Formeln einerseits geschickt bearbeiten und anderseits effektiv speichern zu können.

Der SAT-Lancer benötigt hierfür deutlich weniger Fläche und kann wesentlich größere SAT-Instanzen handhaben als bisherige Hardware SAT-Solver. Wir gratulieren

sehr herzlich zum Best Poster Award!

Foto: Universität Bremen / DFKI GmbH

Rolf Drechsler ist Adjunct Professor am Indian Statistical Institute

Rolf Drechsler ist Adjunct Professor am Indian Statistical Institute

Rolf Drechsler wurde am 7. Juni 2018 zum Adjunct Professor am Indian Statistical Institute (ISI) in Kolkata (Indien) ernannt. Der Festakt fand im Kontext des

"Symposium on Algorithms, Architectures and Applications: Special Focus on Electronic Design Automation" statt, auf dem Rolf Drechsler einen eingeladenen

Vortrag zum Thema "Design and Verification of Cyber-Physical Systems - Challenges and Recent Developments" hielt. Die auf zwei Jahre ausgelegte Gastprofessur

umfasst zwei Aufenthalte pro Jahr am Indian Statistical Institute (ISI). Dabei ist er der Gruppe "Advanced Computing & Microelectronics", die zur "Computer and

Communication Sciences Division" gehört, zugeordnet. Wir freuen uns sehr über diese Auszeichnung!

Mehr Informationen finden Sie hier.

Foto: Universität Bremen / DFKI GmbH

Keynote beim 3rd International Verification and Security Workshop (IVSW) in Spanien

Keynote beim 3rd International Verification and Security Workshop (IVSW) in Spanien

Im Rahmen des 3rd International Verification and Security Workshop (IVSW), der vom 02.-04. Juli in Platja d'Aro, Costa Brava (Spanien) stattfand, hielt

Rolf Drechsler eine Keynote mit dem Titel "Towards Self-Explaining Digital Systems: A Design Methodology for the Next Generation". In seinem Vortrag

zeigte er Möglichkeiten auf, wie selbsterklärende Systeme methodisch und konzeptuell realisiert und implementiert werden können, und gab einen Ausblick

auf Anwendungen in den Bereichen Selbst-Verifikation und Rekonfiguration.

Vorträge für eine breite Zuhörerschaft

Vorträge für eine breite Zuhörerschaft

Vorträge für Personen, die im gleichen thematischen Feld arbeiten, gehören für Wissenschaftler zu einer immer wiederkehrenden Aufgabe. Als Kontrapunkt

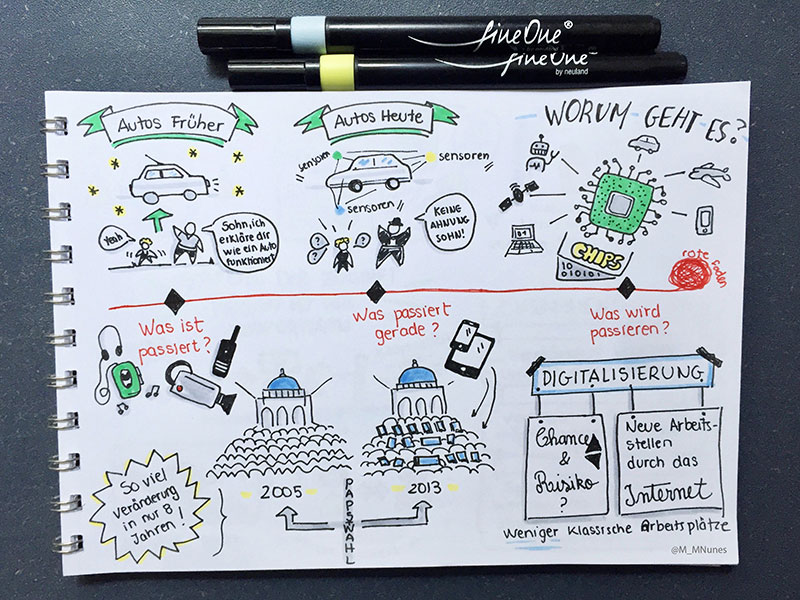

dazu nutzt Rolf Drechsler vielfältige Gelegenheiten, Vorträge für Nicht-Fachleute zu halten. So besuchte er am 21. Juni die European Business School in

Wiesbaden mit einem Vortrag zum Thema "Design and Verification of Cyber-Physical Systems". Sein Vortrag in der Reihe "Wissen um 11" im Haus der Wissenschaft

am 25.08.2018 hatte den Titel "Die Welt von morgen erfahren und die heutige verstehen - spielerisch und mit Humor".

Zeichnung: Maria Manuel Nunes

Nśrdman erreicht breite Leserschaft

Nśrdman erreicht breite Leserschaft

Bereits im letzten Newsletter berichteten wir über die Comicreihe "Nśrdman". Nach einer Pressemitteilung der dpa im Mai wurde das Thema vielfach aufgegriffen,

so berichteten beispielsweise neben RTL, Sat.1 und Nordkurier auch Welt und Focus über unsere Comics. Auch die lokale Presse berichtete,

so beispielsweise das "Horner Magazin" (Ausgabe Juli/August 2018) mit einem sechs Seiten ausführlichen Artikel. Wir freuen uns sehr über dieses Interesse und

werden weiterhin unterhaltsame Comics zu technischen Themen liefern!

Website || Twitter | Instagram | Facebook

Auch im vergangenen Semester konnten wir eine Reihe von Arbeiten auf hochrangigen Konferenzen publizieren, besonders möchten wir auf unsere zahlreichen Publikationen in Journals hinweisen. Im Folgenden präsentieren wir eine Auswahl unserer aktuellen Publikationen und verweisen interessierte Leserinnen und Leser auf die Übersicht der AGRA-Publikationen.

Received Best Poster Award

Workshops, Konferenzen und Zeitschriften repräsentieren die wesentlichen Plattformen zum Austausch wissenschaftlicher Ergebnisse. Mitglieder der Arbeitsgruppe sind in verschiedenen Gremien für Konferenzen und Zeitschriften tätig, unter anderem

- Rolf Drechsler als Tutorial & Special Session Chair der ICCAD 2018, sowie General Chair des ETS 2018 und des IWSBP 2018.

- Daniel Große als Special Session Chair der FDL 2018, Special Session Program Committee Member des DSD 2018, Technical Program Committee Member der DATE 2019 und DAC 2019, und als Program Committee Member des IWSBP 2018.

- Sebastian Huhn als Local & Financial Chair des ETS 2018 sowie Organizing Committee Member der TSS 2018.

- Lisa Jungmann als Web & Electronic Media Chair des ETS 2018.