Nr. 19 | Sommersemester 2019

Liebe Leserinnen

und Leser,

Liebe Leserinnen

und Leser,

in diesem Newsletter informieren wir unter anderem über zwei neue Forschungsprojekte und über Ergebnisse in laufenden Projekten. Eine besondere Anerkennung ist es, dass die Publikation über das Werkzeug "PolyCleaner" mit dem Best Paper Award der ICCAD ausgezeichnet wurde. Neben diesen Erfolgen in der Forschung freuen wir uns sehr, dass auch unser Engagement in der Lehre Anerkennung findet: Für das studentische Projekt "BugRunner" wurde uns der Berninghausen-Preis in der Kategorie "Hervorragende, innovative Lehrveranstaltung" verliehen.

Ich wünsche Ihnen eine inspirierende Lektüre

und einen guten Start in den Sommer!

Neues Projekt zur Identifizierung von Prozessfenstern für neuartige Legierungen

Neues Projekt zur Identifizierung von Prozessfenstern für neuartige LegierungenIn einem neuen, vom MAPEX Center for Materials and Processes der Universität Bremen geförderten Interdisciplinary Research Impulse Project (Laufzeit: 01.12.2018 bis 31.12.2019) werden Techniken entwickelt, die eine schnellere Entwicklung von neuen Legierungssystemen ermöglichen. Selektives Laserschmelzen ist ein additives Fertigungsverfahren, bei dem ein Werkstoff in Pulverform in einer dünnen Schicht auf einer Grundplatte aufgebracht wird. Durch Laserstrahlung wird dieser pulverförmige Werkstoff geschmolzen und bildet nach Erstarrung eine feste Materialschicht. Gegenüber konventionellen Gussverfahren bringt das Laserschmelzen eine Reihe von Vorteilen mit sich, allerdings kommt bislang nur eine geringe Anzahl an Gusslegierungen zum Einsatz. Ein wesentliches Hindernis stellt dabei der hohe Aufwand zur Identifizierung von passenden Prozessfenstern für neuartige Legierungen dar. In diesem Projekt werden defekte Strukturen sowie Wechselwirkungen zwischen verschiedenen Prozessparametern systematisch analysiert. Dies bildet eine Grundlage für die Identifizierung optimierter Prozessparameter, mit dem Ziel, das gesamte Materialpotential ausschöpfen zu können.

Neues DFG-Projekt

zur Synthese und Verifikation von Logic-In Memory Architekturen

Neues DFG-Projekt

zur Synthese und Verifikation von Logic-In Memory ArchitekturenMit rund 300.000 Euro fördert die Deutsche Forschungsgemeinschaft (DFG) in den kommenden drei Jahren ein Projekt mit dem Titel "HDL-basierte Synthese und Verifikation

für programmierbare Logic-In Memory Architektur", das die Fertigung von Speicherbausteinen ermöglicht, die Daten nicht nur speichern, sondern auch verarbeiten können.

Prozessoren werden in einer Größenordnung von wenigen Nanometern gebaut - die Rechnerarchitektur stößt damit an physikalische Grenzen und einen Wendepunkt, der neue Lösungen

zur Speicherung und Verarbeitung von Daten erfordert. Ein Ansatz, der in diesem Projekt verfolgt wird, besteht darin, mit Hilfe des sogenannten Logic-In Memory Computing

die Grenze zwischen Speicher und Berechnungseinheit aufzuheben, was eine gleichzeitige Speicherung und Verarbeitung von Daten ermöglicht. Das Projekt befasst sich konkret

mit der Frage, wie solche Schaltungen gebaut werden können. Zusätzlich soll es ermöglicht werden, zeitgleich mit der Fertigung auch die Verifikation durchzuführen.

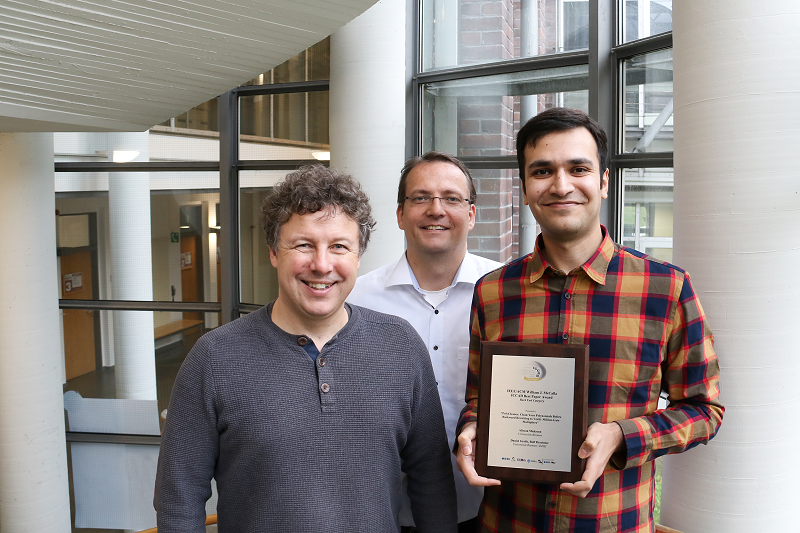

Multiplizieren - aber richtig! IEEE/ACM William J. McCalla ICCAD Best Paper Award

Multiplizieren - aber richtig! IEEE/ACM William J. McCalla ICCAD Best Paper AwardArithmetische Schaltkreise wie Multiplizierer kommen heute in jedem Prozessor vor. Sind sie fehlerhaft, verursacht dies hohe Kosten. Wie sich die funktionale

Korrektheit solcher Schaltkreise nachweisen lässt, damit haben sich Alireza Mahzoon, Daniel Große und Rolf Drechsler beschäftigt. Für ihre Forschungsarbeit wurden

sie im November 2018 mit dem Best Paper Award der International Conference on Computer Aided Design (ICCAD), einer der führenden Tagungen auf dem Gebiet des

Schaltkreisentwurfs, in San Diego (USA) ausgezeichnet.

Die Multiplikation von zwei Zahlen mag für Grundschulkinder eine einfache Aufgabe sein, für Computer ist sie jedoch, insbesondere bei großen Zahlen, rechenintensiv.

Gerade wenn eine Berechnung sehr schnell erfolgen oder der Stromverbrauch möglichst gering ausfallen soll, werden nach diesen Kriterien optimierte Schaltkreise,

sogenannte Multiplizierer, eingesetzt. Der Fokus der ausgezeichneten Arbeit mit dem Titel "PolyCleaner: Clean your Polynomials before Backward Rewriting to

Verify Million-gate Multipliers" liegt auf der Verifikation von Multiplizierern, also dem Nachweis der korrekten Funktion solcher Schaltkreise. Diese Arbeit

erlaubt es nun erstmalig, die Korrektheit von Multiplizierern mit mehr als einer Million Gattern nachzuweisen. Dafür wurden neue theoretische Erkenntnisse

erarbeitet und im "PolyCleaner" implementiert. Dieses Werkzeug verwendet Polynome für die Darstellung der Verifikationsaufgabe. Allerdings führte die Verwendung

von Polynomen bisher aufgrund zahlreicher redundanter Terme zu einem explosionsartig ansteigenden Speicherplatzbedarf. Dank PolyCleaner wird genau dies verhindert:

Redundante und hundertausendfach auftretende Terme werden zunächst beseitigt, so dass anschließend der automatische Korrektheitsnachweis problemlos gelingen kann.

Innovativer Ansatz in der Verifikationsmethodik - Best Paper Award der DVCon Europe

Innovativer Ansatz in der Verifikationsmethodik - Best Paper Award der DVCon EuropeElektronische Systeme werden immer komplexer und bestehen meist aus digitalen und analogen Komponenten. Der Aufwand für die Verifikation solcher Systeme ist jedoch

kaum zu beherrschen. In der Publikation mit dem Titel "Using Constraints for SystemC AMS Design and Verification" ist es Daniel Große und Muhammad Hassan (Forschungsbereich

Cyber-Physical Systems des Deutschen Forschungszentrums für Künstliche Intelligenz DFKI) - unter Leitung von Rolf Drechsler - in Zusammenarbeit mit Thilo Vörtler und Karsten

Einwich von der COSEDA Technologies GmbH gelungen, einen Lösungsansatz für dieses Problem aufzuzeigen. Dafür wurden sie auf der DVCon Europe 2018 in München mit dem Best

Paper Award ausgezeichnet.

Ziel der Forschungsarbeit ist es, die automatische Verifikation von gemischten analog-digitalen Systemen in einer möglichst frühen Entwurfsphase deutlich zu beschleunigen.

Hierbei setzen wir auf Constrained Random Verification, die bereits sehr erfolgreich für die Verifikation rein digitaler Systeme zum Einsatz kommt. In frühen Entwurfsphasen

kommen virtuelle Prototypen zum Einsatz, die eine effiziente Simulation von Anwendungsszenarien des Gesamtsystems erlauben. Das Ziel der Arbeit bestand darin, die Erfolge,

die durch die Constrained Random Verification rein digitaler Systeme möglich sind, auch für heterogene Systeme zu erreichen. Dafür wurde die bereits im Forschungsbereich

entwickelte Verifikationsumgebung CRAVE (Advanced Constrained RAndom Verification Environment for SystemC) für die Lösung von analogen Bedingungen erweitert.

Sommersemester 2019

Abschlussarbeiten

Abschlussarbeiten stellen den Höhepunkt des Studiums dar. In der Arbeitsgruppe kann dabei eine Vielzahl an verschiedenen Themen bearbeitet werden. An dieser Stelle präsentieren wir die Abschlussarbeiten, die im letzten Semester in unserer Gruppe abgeschlossen wurden.

- Jil Tietjen, Symbolische Ausführung eines RISC-V-Prozessors, Master, 2018

- Niklas Bruns, Erkennung von Hardware-Trojanern in SystemC HLS Modellen durch Coverage-getriebenes Fuzzing, Master, 2018

- Niels Jeurissen, Robustheit von Methoden zur Bilderkennung am Beispiel von Straßen bei schlechter Witterungsbedingung, Bachelor, 2018

- Philipp Kiener, Designing a communication protocol for realtime manipulation of digital microfluidic biochips, Bachelor, 2018

- Malte Christian Struck, Ein Service-Discovery-Protokoll für Netze heterogener Sensoreinheiten, Master, 2018

- Tom Vincent Peters, Mastering the game of Dots and Boxes with deep neural networks and tree search, Master, 2018

- Hauke Edeler, Lösung komplexer DMFB-Routenprobleme per Reinforcement Learning, Master, 2018

- Kevin Leonhard Schneider, Improving the Heuristics for One-Pass-Synthesis of Digital Microfluidic Biochips, Master, 2018

- Carmen Naber, Konzeptionierung und Umsetzung eines adaptiven mobilen Learning-Content-Management-Systems für Schulen, Bachelor, 2019

Du hast Interesse, deine Abschlussarbeit in der Arbeitsgruppe Rechnerarchitektur anzufertigen?

Dann melde dich einfach bei uns: drechsler@uni-bremen.de.

Berninghausen-Preis für die Lehrveranstaltung BugRunner

Berninghausen-Preis für die Lehrveranstaltung BugRunner

Für unser studentisches Bachelor-Projekt "BugRunner" wurde uns der Berninghausen-Preis 2018 in der Kategorie "Hervorragende, innovative Lehrveranstaltung"

verliehen. Unser Team - Rolf Drechsler, Cornelia Große, Oliver Keszöcze, Kenneth Schmitz und Jannis Stoppe - wurde von den Studierenden vorgeschlagen und

von einer Jury ausgewählt. Inhaltlich arbeiteten wir mit den Studierenden daran, Fehler in Firmware zu identifizieren. Unser Lehrkonzept, diese abstrakten

Lerninhalte am Beispiel von alten Spielekonsolen anschaulich und "greifbar" zu machen, überzeugte die Studierenden und die Jury.

Mit dem durch die Universität Bremen und die "unifreunde - Freunde der Universität Bremen und der International University Bremen e.V." verliehenen Preis

werden besondere Leistungen in der universitären Lehre ausgezeichnet. Alle Mitglieder der Universität können Lehrende dafür vorschlagen. Eine Auswahlkommission

wählt nach sorgfältiger Prüfung und Einholung von Stellungnahmen die Preisträgerinnen und Preisträger aus und schlägt sie dem Akademischen Senat zur

Beschlussfassung vor.

Wir freuen uns sehr über diese großartige Auszeichnung und Anerkennung unseres Engagements in der Lehre!

Foto: Harald Rehling/Universität Bremen

Erfolgreiche Verteidigung der Dissertation von Saeideh Shirinzadeh

Erfolgreiche Verteidigung der Dissertation von Saeideh Shirinzadeh

Dr. Saeideh Shirinzadeh verteidigte am 01.10.2018 erfolgreich ihre Dissertation mit dem Titel "Synthesis and Optimization for Logic-in-Memory Computing Using

Memristive Devices". In-Memory-Computing ist ein neu aufkommendes Computing-Paradigma, das es ermöglicht, Berechnungen innerhalb von Speichern durchzuführen.

Dies steht im Gegensatz zu heutigen Computerarchitekturen, bei denen die Daten in zwei getrennten Einheiten verarbeitet und gespeichert werden. Dies erfordert

eine Kommunikation zwischen dem Prozessor und dem Speicher, was eine hohe Latenz verursacht und daher die Leistung verringert. In ihrer Dissertation adressiert

Saeideh Shirinzadeh dieses Problem, indem sie Design-Ansätze für In-Memory-Computing unter Verwendung einer fortschrittlichen non-volatile Speichertechnologie

vorschlägt. Sie erarbeitete eine umfassende Umgebung für die Entwicklung und Automatisierung effizienter Hardware- und Computerarchitekturen mit

Logik-in-Memory-Computing, mit dem Ziel, neue Anwendungen, die mit großen Datenmengen arbeiten, zu beschleunigen. Diese Arbeiten von Saeideh Shirinzadeh

bildeten die Grundlage für einen Forschungsantrag mit dem Titel "HDL-basierte Synthese und Verifikation für programmierbare Logic-In Memory Architektur",

der von der DFG gefördert wird - nähere Informationen hierzu finden Sie in der Rubrik "Forschung".

Wir gratulieren sehr herzlich und wünschen weiterhin viel Erfolg!

Erfolgreiche Verteidigung der Dissertation von Arighna Deb

Erfolgreiche Verteidigung der Dissertation von Arighna Deb

Dr. Arighna Deb verteidigte am 17.12.2018 erfolgreich seine Dissertation mit dem Titel "Logic Synthesis Techniques for Optical Circuits". Optische Schaltungen

stellen eine alternative Technologie zu bisherigen Schaltungen dar, welche nicht mit elektrischen, sondern mit optischen Signalen arbeiten. Während elektrische

Signale digitale Schaltungen über "Strom an" für die 1 und "Strom aus" für die 0 beschreiben, geschieht dies in optischen Schaltungen über "Licht an" und "Licht

aus". Insbesondere für Anwendungen im Bereich der Kommunikation oder in so genannten Interconnects ist diese Form der bisherigen Darstellung oft deutlich überlegen.

Mit der neuen Technologie ändern sich aber auch bestimmte physikalische Anforderungen. Entsprechend können konventionelle Syntheseansätze nicht direkt genutzt werden,

sondern müssen darauf angepasst werden. In seiner Dissertation hat sich Dr. Deb intensiv mit entsprechenden Verfahren für die Synthese optischer Schaltungen befasst.

Diese berücksichtigen explizit die neuen Beschreibungsformen und Kostenmaße und erlauben eine effiziente und technologieorientiere Synthese optischer Schaltungen.

Wir gratulieren sehr herzlich und wünschen weiterhin alles Gute!

Neuer Mitarbeiter: Steffen Frerix

Neuer Mitarbeiter: Steffen Frerix

Seit dem 15.02.2019 verstärkt Steffen Frerix unser Team. Er beschäftigt sich mit HDL-basierter Synthese von neuartigen In-Memory Computerarchitekturen, bei denen

Datenverarbeitung in persistenten Speicherelementen stattfindet. Dabei konzentriert er sich auf effiziente Synthese auf hoher Abstraktionsebene und formale

Verifikation der resultierenden Implementierung.

Wir freuen uns sehr auf die Zusammenarbeit!

Netzwerktreffen des MINTforum Bremen

Netzwerktreffen des MINTforum Bremen

Am 30.10.2018 hielt Rolf Drechsler beim Netzwerktreffen des MINTforum Bremen in der Hochschule Bremerhaven ein Impulsreferat zur Einführung in das

Schwerpunktthema "Digitalisierung, virtuelle Welten, Künstliche Intelligenz - wie wird sich unsere Arbeit und unser Leben verändern". Das Treffen

diente zur Vorbereitung eines MINT-Tags.

Nśrdman-Comics auch in Print

Nśrdman-Comics auch in Print

Seit Januar 2019 erscheinen unsere Nśrdman-Comics monatlich im "Stadtmagazin". Auch wenn uns

jeder echte Nerd selbstverständlich auf Twitter, Facebook

und Instagram folgt, freuen wir uns dennoch sehr über diese Gelegenheit,

unsere Begeisterung für Technik auch mit Menschen teilen zu können, die (bisher) lieber mit Papier als mit Computern interagieren. Mit einer Auflage

von 91.000 Exemplaren erreichen wir damit eine breite Öffentlichkeit in Bremen.

Auch im vergangenen Semester konnten wir eine Reihe von Arbeiten auf hochrangigen Konferenzen publizieren, besonders möchten wir auf die Arbeit zum "PolyCleaner" hinweisen, die mit dem Best Paper Award der ICCAD ausgezeichnet wurde. Darüber hinaus erschienen bei Springer zwei Monografien und ein Herausgeberwerk. Im Folgenden präsentieren wir eine Auswahl unserer aktuellen Publikationen und verweisen interessierte Leserinnen und Leser auf die Übersicht der AGRA-Publikationen.

Workshops, Konferenzen und Zeitschriften repräsentieren die wesentlichen Plattformen zum Austausch wissenschaftlicher Ergebnisse. Mitglieder der Arbeitsgruppe sind in verschiedenen Gremien für Konferenzen und Zeitschriften tätig, unter anderem

- Rolf Drechsler als Associate Editor von IEEE Transactions on VLSI Systems (TVLSI) sowie als Vice Program Chair der ICCAD 2019

- Daniel Große als (Technical) Program Committee Member von CODES+ISSS 2019, ETS 2019, GLSVLSI 2019, MBMV 2019, DAC 2019