GenArc

Im Projekt GenArC geht es um die automatische Generierung von arithmetischen Schaltkreisen. Kernbestandteile sind die Implementierung einer einfachen RISC-V Architektur, die Entwicklung der Architektur eines AES Hardwarebeschleunigers, sowie das tatsächliche Ausführen der Schaltungen auf verschiedenen FPGAs. Zusätzlich liegt ein großer Fokus auf dem Testen und der Verifikation der realisierten Schaltungen.

Zugrunde liegt die Software ArithsGen, in welcher Schaltkreise auf Grundlage einer Beschreibung durch Python-Code generiert werden können. Diese Software wurde im Rahmen des Projekts weiterentwickelt.

RISC-V

Im Zuge der Implementierung einer Rechnerarchitektur wurde sich für die RISC-V Befehlssatzarchitektur entschieden. Einige der entscheidenen Vorteil dieser sind ihr open source Charakter, Modularität und Einfachheit. Um die Simulation einer Microarchitektur zu implementieren, die dem RISC-V Standard gerecht wird, wurde die bestehende ArithsGen Software verwendet und erweitert. Im Speziellen wurde ArithsGen um die fehlenden Schaltungen ergänzt, um die I und M Extensions zu vervollständigen.

AES

Datensicherheit wird in unser vernetzten Welt immer wichtiger.

Was bietet sich also mehr an, als die Verschlüsselung von Daten in einen dedizierten Chip auszulagern. So kann einerseits die Verschlüsselungsgeschwindigkeit erhöht werden, und andererseits wird das gesamte Verfahren sicherer, weil es weniger Angriffspunkte während der Verschlüsselung bietet.

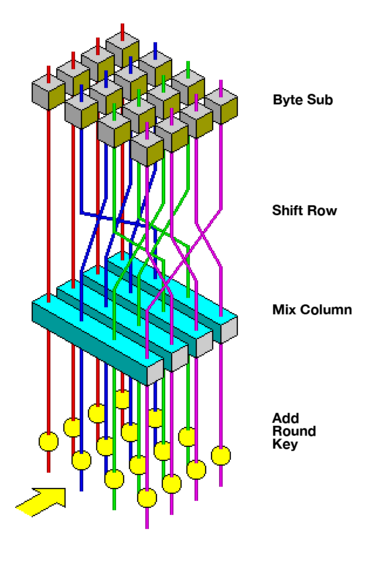

Es wurde sich dafür entschieden das symmetrische Verfahren AES, den Advanced Encryption Standard, umzusetzen. Dieser aktuelle Standard zeichnet sich durch hohe Verschlüsselungsgeschwindigkeiten aus und lässt sich größtenteils auf die, in Hardware einfach zu realisierenden, Operationen Bitshifting und XOR herunterbrechen.

Ein großer Vorteil für die Umsetzung in Hardware und Geschwindigkeit von AES, aber auch Sicherheitskritikpunkt, sind die sehr einfachen erwähnten mathematischen Operationen.

Test & Verifikation

Aufgabe im Bereich Verifikation und Tests war vor allem das möglichst effiziente Prüfen erstellter Schaltkreise auf Korrektheit.

Um sicherzugehen, dass ein Schaltkreis richtig funktioniert, eignen sich verschiedene Herangehensweisen. Ein naiver Ansatz wäre es, alle möglichen Eingabekombinationen durchzuprobieren und die Ergebnisse zu prüfen. Für kleinere Schaltkreise ist dieser Ansatz noch machbar, aber nicht effizient. Denn nähert man sich verbreiteten Größen, wie 32- oder 64-bit, “explodiert” der benötigte Zeitaufwand exponentiell. De facto ist das Durchprobieren unter diesen Umständen nicht mehr machbar. Daher wurde sich einiger Methoden bedient um auch größere Schaltkreise verifizieren zu können.

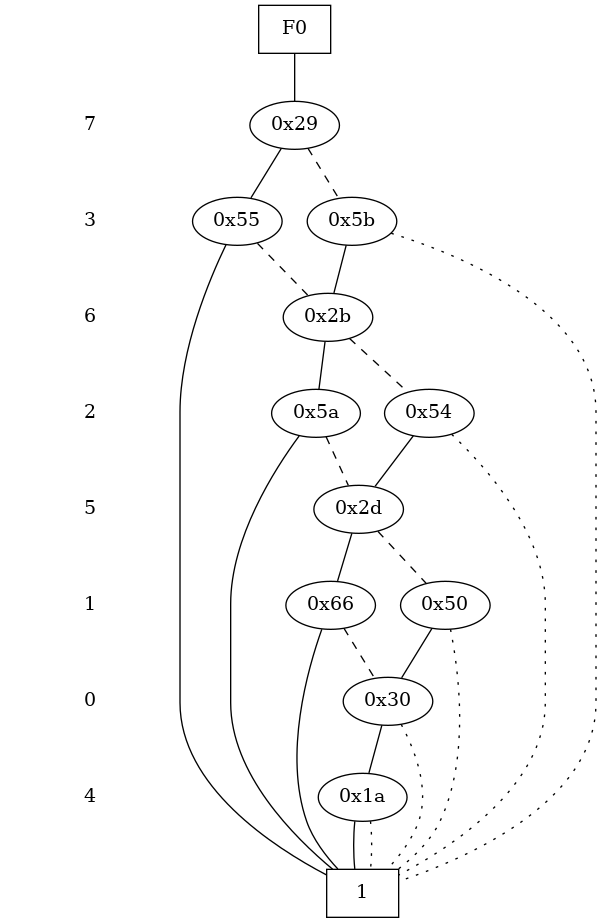

Eine solche Herangehensweise sind Binary Decision Diagrams, die Boolsche Funktionen als Graphen repräsentieren. Ein reduziertes und geordnetes Binary Decision Diagram (ROBDD) ist minimal und somit immer eindeutig. Das heißt, wenn man zwei Schaltungen entwirft, die das gleiche berechnen, jedoch vielleicht aus Performancegründen unterschiedlich aufgebaut sind, kann mithilfe ihrer ROBDDs überprüft werden, ob diese Schaltungen logisch identisch sind. Mehr noch: dadurch wird sogar mathematisch bewiesen, dass sie logisch identisch sind.

FPGA

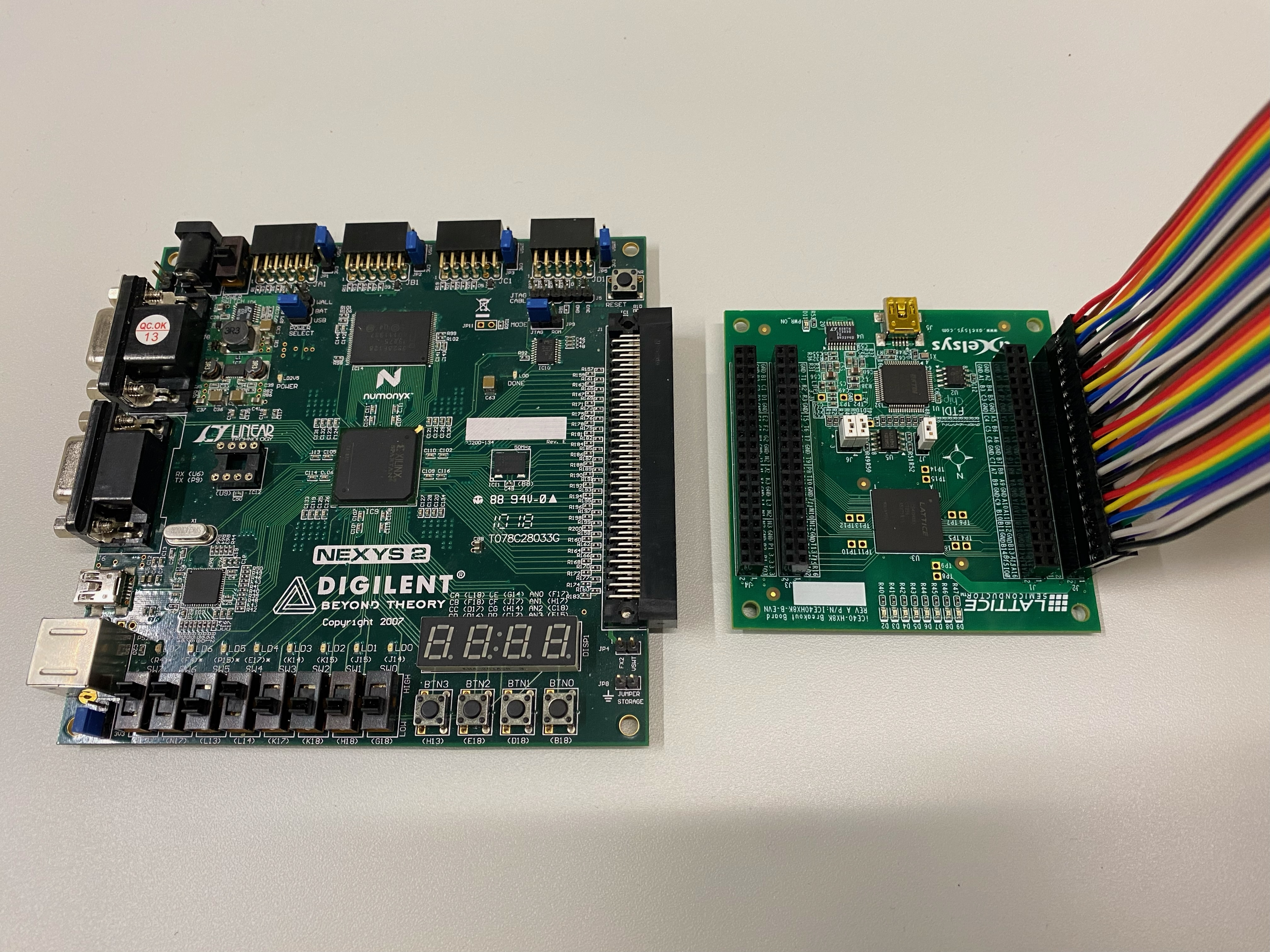

FPGAs (Field Programmable Gate Arrays) sind Prozessoren welche dadurch ausgezeichnet sind, dass die Anordnung der Gatter variabel und programmierbar ist. Das bedeutet, dass verschiedene Schaltungen bzw. Architekturen auf diese geladen und getestet werden können, ohne dass für jede Iteration ein neuer Chip hergestellt werden muss.

Für das Projekt stehen FPGAs von zwei Herstellern zur Verfügung. Das Ziel ist hierbei, die erstellten Schaltkreise auf die reale Hardware abzubilden. Um das zu erreichen, muss ein für das Board spezifischer Bitstream erzeugt und auf den Chip hochgeladen werden. Ein zentraler Aspekt hierbei ist die Automatisierung des Prozesses, unabhängig vom Hersteller des Boards.

Um Inputs geben und die Outputs sehen zu können müssen unter anderem Schalter und Displays an das Board angeschlossen werden.